# A 280-GHz Schottky Diode Detector in 130-nm Digital CMOS

Ruonan Han, Yaming Zhang, Dominique Coquillat, Hadley Videlier, Wojciech Knap, Elliott Brown, Fellow, IEEE, and Kenneth K. O, Fellow, IEEE

Abstract—A 2 × 2 array of 280-GHz Schottky-barrier diode detectors with an on-chip patch antenna ( $255 \times 250 \ \mu m^2$ ) is fabricated in a 130-nm logic CMOS process. The series resistance of diode is minimized using poly-gate separation (PGS), and exhibits a cut-off frequency of 2 THz. Each detector unit can detect an incident carrier with 100-Hz ~ 2-MHz amplitude modulation. At 1-MHz modulation frequency, the estimated voltage responsivity and noise equivalent power (NEP) of the detector unit are 250 V/W and 33 pW/Hz<sup>1/2</sup>, respectively. An integrated low-noise amplifier further boosts the responsivity to 80 kV/W. At supply voltage of 1.2 V, the entire chip consumes 1.6 mW. The array occupies  $1.5 \times 0.8 \ mm^2$ . A set of millimeter-wave images with a signal-noise ratio of 48 dB is formed using the detector. These suggest potential utility of Schottky diode detectors fabricated in CMOS for millimeter wave and sub-millimeter wave imaging.

*Index Terms*—CMOS, detector, imaging, NEP, on-chip patch antenna, responsivity, Schottky barrier diode, terahertz.

# I. INTRODUCTION

**R** ESEARCH at the terahertz frequency range (100 GHz– 10 THz) of electromagnetic spectrum has been active for potential applications in imaging including that for concealed weapon detection, aviation assistance and cancer detection, spectroscopy, short range radar, secured high-speed data communication, and others [1]–[3]. For all these applications, a detector is a fundamental building block. THz detectors fabricated in CMOS for imaging in particular have received a great deal of attention for their potential for low cost, high yield and excellent capability of integration with other signal processing circuits. Based on the Dyakonov-Shur plasma wave detection theory [4], the first sub-THz silicon FET detector was demonstrated in 2004 by Knap *et al.* [5], [6]. The first focal plane FET detector array (3 × 5 pixels) in 0.25  $\mu$ m CMOS was reported

Y. Zhang and K. K. O are with the Texas Analog Center of Excellence and Department of Electrical Engineering, University of Texas, Dallas, TX 75080 USA.

D. Coquillat, H. Videlier, and W. Knap are with the Université Montpellier 2 and CNRS, TERALAB-GIS, L2C UMR 5221, 34095 Montpellier, France.

E. Brown is with the Department of Physics and Electrical Engineering, Wright State University, Dayton, OH 45435 USA.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2011.2165234

for imaging at 650 GHz by Lisauskas and Öjefors *et al.* in 2009 [7], [8]. More recently, a FET detector fabricated in a 65-nm SOI CMOS technology using high resistivity substrates was reported to achieve an NEP (Noise Equivalent Power) of 50 pW/Hz<sup>1/2</sup> at 650 GHz [9].

For their high speed and fabrication simplicity, Schottky barrier diodes (SBDs) have been used to implement an RF detector for the past century and continue to play an important role. Excellent NEP performance for III-V semiconductor SBD has been reported ( $^{20}$  pW/Hz<sup>1/2</sup> at 800 GHz [10] and 1.4 pW/Hz<sup>1/2</sup> at 100 GHz [11]). By using interband tunneling, a heterojunction backward diode presented in [12] demonstrated 49.7 kV/W responsivity and 0.18 pW/Hz<sup>1/2</sup> NEP at 94 GHz. It was reported in 2005 that a Shallow Trench Separated (STS) Schottky barrier diode with 1.5-THz cut-off frequency could be fabricated in foundry 130-nm digital CMOS without any process modifications [13]. Using this device structure, a millimeterwave detector [14] and a frequency doubler [15] were demonstrated, but the noise performance and responsivity of the detector were not characterized. The cut-off frequency is increased to above 2-THz employing Polysilicon-Gate Separated (PGS) Schottky diodes [16], [17] in the same 130-nm CMOS. Using these diodes, a 280-GHz detector has been demonstrated [18], however the measured responsivity fluctuates significantly with frequencies, and the peak value is over three times smaller than that in the simulation. To better understand these, the detector was characterized with a higher power source (29 mW compared with 82  $\mu$ W in [18]) that allowed measurements at larger source-to-detector separation with reduced standing wave effects. The measured total responsivity increases to 80 kV/W (or 250 V/W without on-chip amplification) which matches the simulation well. In combination with this and using higher modulation frequency (1 MHz compared with 25 kHz in [18]), this paper reports single cell NEP of 33 pW/Hz<sup>1/2</sup>.

In Section II, Schottky diode and detection using the diode are presented. Section III discusses the diode detector design. The measurements including responsivity and noise performance as well as images formed with the detector are presented in Section IV. Finally, conclusions including comparisons to previously reported detectors are discussed in Section V.

#### II. SCHOTTKY DIODE AND SQUARE-LAW DETECTION

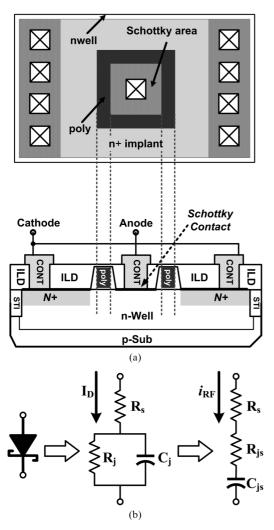

A PGS SBD in digital foundry CMOS was first reported in 2009 [16]. Its unit-cell cross section and top view are shown in Fig. 1. A polysilicon gate is used to separate the anode and cathode. Compared to STS SBD, the current path between the Schottky junction and  $n^+$  cathode region in a PGS Schottky diode is shorter. Therefore for a 16-unit-cell test structure, the

Manuscript received February 15, 2011; revised July 21, 2011; accepted July 28, 2011. Date of publication September 29, 2011; date of current version October 26, 2011. This paper was approved by Associate Editor Anthony Chan Carusone. This work was supported in part by C2S2 and FCRP.

R. Han was with the Department of Electrical and Computer Engineering, University of Florida, Gainesville, FL 32611 USA. He is now with the Department of Electrical and Computer Engineering, Cornell University, Ithaca, NY 14853 USA.

Fig. 1. Poly-Gate-Separated Schottky-barrier diode in 130-nm CMOS process: (a) cross section and top view (b) simplified model of a biased diode. The figures in (a) are not drawn to scale.  $R_s$  and  $C_j$  are the series resistance and junction capacitance of the diode,  $R_j$  represents the dynamic resistance  $(1/g_m)$  of diode, and  $R_{js}$  and  $C_{js}$  are the equivalent series components of the diode.

series resistance,  $R_s$  (see the equivalent model in Fig. 1(b)) drops from 13 to 8  $\Omega$ . Due to the polysilicon gate to contact spacing design rule, the unit-cell Schottky area increases from  $0.32 \times 0.32 \ \mu\text{m}^2$  (STS SBD) to  $0.4 \times 0.4 \ \mu\text{m}^2$  (PGS SBD), which increases the junction capacitance,  $C_j$  from 8 to 10 fF. But the overall cut-off frequency,  $f_{\rm T} = 1/(R_s \cdot C_j)$  increases from 1.5 to 2 THz.

When a small AC signal is applied, a Schottky diode generates DC voltage proportional to the signal power due to its second and other even order terms associated with nonlinearity. For a device with nonlinear I - V relationship, i = f(v), the ideal current responsivity  $\Re_{i,0}$  which is the ratio between the rectified DC current  $\Delta i$  and the input power  $P_{in}$ , is [19]

$$\Re_{i,0} = \frac{\Delta i}{P_{in}} = \frac{f^{(2)}(v)}{2f^{(1)}(v)} \tag{1}$$

where  $f^{(1)}(v)$  and  $f^{(2)}(v)$  are the first and second derivatives of f(v). For Schottky diodes,  $i_D = f_D(v_D) = I_s \cdot (e^{qv_D/nk_BT} - 1)$ , where  $I_s$  is the diode reverse saturation current,  $k_B$  is Boltzmann's constant and n is the diode ideality factor. The measured

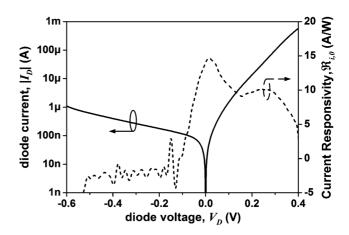

Fig. 2. Measured I - V characteristic of a 16-unit-cell PGS Schottky diode (solid line), and the calculated ideal current responsivity (dashed line).

I - V characteristics of the PGS SBD are shown in Fig. 2. The extracted saturation current,  $I_s$  and ideality factor, n are 50 nA and 1.35 respectively. Current responsivity extracted using (1) is also plotted in Fig. 2. For  $I_D = 1$  to 100  $\mu$ A, the current responsivity is on the order of 10 A/W, which is significantly larger than that of ~2.6 mA/W for a FET-based detector [8].

The detector in this paper operates in a voltage mode, and the current responsivity can be converted into the voltage responsivity  $\Re_{v,0}$ , which is the product of the current responsivity  $\Re_{i,0}$  and the dynamic diode junction resistance  $R_j$  ( $R_j = 1/g_m = 1/f_D^{(1)}(v_D)$ ).

$$\Re_{v,0} = \frac{\Delta v}{P_{in}} = \frac{\Delta i}{P_{in}} \cdot R_j = \frac{f_D^{(2)}(v_D)}{2\left[f_D^{(1)}(v_D)\right]^2} = \frac{1}{2I_s \cdot e^{\frac{qv_D}{nk_BT}}} = \frac{1}{2(I_D + I_s)}.$$

(2)

From (2), the peak voltage responsivity occurs when diode bias current approaches zero. However, this bias condition is not used for two reasons:

- (i) Due to the low reverse saturation current of the diode (I<sub>s</sub> = 50 nA), junction resistance R<sub>j</sub> at low bias level is too high (~ 700 kΩ) for efficient power matching.

- (ii) High  $R_j$  forms a low-frequency pole with the load capacitance,  $C_L$ , of the detector  $(f_{out,p} = 1/(2\pi R_j C_L))$ , which limits the bandwidth of detector.

Because of these, the diode in this detector design is forward biased. Besides the bias current, the number of diode unit cells in shunt, namely the total diode size must be specified. Note that the previous analysis assumed that all the input RF power is absorbed by  $R_j$ , which is not true in reality due to the finite series resistance  $R_s$  and junction capacitance  $C_j$ . Based on the diode model in Fig. 1(b), the RF power transfer degradation factor  $\xi$  can be expressed as [19]

$$\xi = \frac{P_{total} - P_j}{P_{total}} = 1 - \frac{R_{js}}{R_{js} + R_s}$$

=  $1 - \frac{R_s}{R_j + R_s + R_s^2 R_j^2 C_j^2 \omega^2 / R_s}$

=  $1 - \frac{1}{1 + \frac{R_s}{R_j} + \frac{R_j}{R_s} \cdot \left(\frac{\omega}{\omega_T}\right)^2}$  (3)

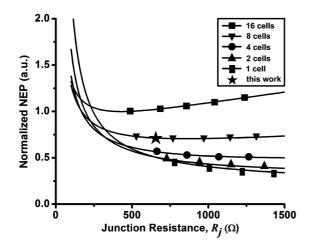

Fig. 3. Calculated NEP of detectors with different diode junction resistance  $R_j$  and the number of unit cells.

Fig. 4. Schematic of the 280-GHz Schottky diode detector.

where  $P_{total}$  and  $P_j$  are the total input power and the power dissipated in  $R_j$ , respectively. At 280 GHz for the PGS, (3) gives a minimum responsivity drop of 22%.

Another key performance metric for the detector, Noise Equivalent Power (NEP), is defined as the input RF power level at which the detector output signal to noise ratio (SNR) is unity for 1-Hz bandwidth. Mathematically, it is the ratio between the output noise voltage spectral density  $(V/Hz^{1/2})$  and detector voltage responsivity. To achieve optimum NEP, the shot and flicker noise generated in diode need to be considered. The power spectrum density (PSD) [19] is

$$\overline{i_n^2}/\Delta f = \frac{4k_B T t_w}{R_j} \left(1 + \frac{f_N}{f}\right) \tag{4}$$

where  $f_N$  is the flicker noise corner frequency, which is normally proportional to the bias current; and  $t_w$  is the white noise temperature ratio (the ratio between the white noise generated from the diode and that from a resistor equal to  $R_j$ ), which is n/2 when forward bias current  $I_D$  is much larger than  $I_s$  [20]. Combining (1)–(3) and the shot noise part of (4), NEP of the diode detector with modulation frequency higher than the 1/fnoise corner frequency is

$$NEP = \frac{R_{j} \cdot \sqrt{i_{n}^{2}/\Delta f}}{R_{j} \cdot \Re_{i,0} \cdot (1-\xi)}$$

$$\approx \frac{4nt_{w}^{1/2} \cdot (k_{B}T)^{3/2}}{q} \cdot \frac{1 + \frac{R_{s}}{R_{j}} + \frac{R_{j}}{R_{s}} \left(\frac{\omega}{\omega_{T}}\right)^{2}}{R_{j}^{1/2}}.$$

(5)

Fig. 5. (a) Top and (b) cross section views of the patch antenna. The slots in M1 and M2 layers are required by the design rules.

$R_s$  and  $C_j$  scale inversely and linearly with the number of unit cells. A set of NEP plots based on (5) are plotted in Fig. 3.

The scalability of PGS SBD model, which is based on measurements of a 16 unit-cell test structure, is questionable. As a smaller number of unit cells is chosen, the diode impedance becomes more susceptible to any possible interconnect parasitics. For instance, if a single cell diode with scaled  $C_j$  of 0.63 fF is chosen, simulations indicate that a 1 fF interconnect parasitic shunt capacitance could result in a reflection loss of -5 dB. As a compromise, the unit cell number of 8 that results around the median NEP is chosen for the design, though Fig. 3 indicates that fewer diode cells lead to lower NEP. Additionally, Fig. 3 also shows that NEP does not change significantly once the junction resistance increases above 500  $\Omega$ , so the dynamic diode junction resistance is chosen to be 600–700  $\Omega$ , which requires a bias current of ~ 50  $\mu$ A.

# III. 280-GHz DIODE DETECTOR DESIGN

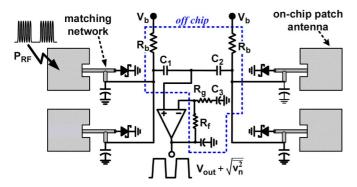

A schematic of the diode detector is shown in Fig. 4. Four detector cells are fabricated on the same die. It will be shown in Section III-C of this section that for uniformly-distributed radiation power density, combining the outputs of four cells could increase the signal to noise ratio (SNR) of image by 6 dB. In general, each detector cell collects the radiation signal at 280 GHz through one on-chip patch antenna, and then rectifies the signal using the diode square-law detection discussed earlier to generate the baseband signal. Similar to other radiation detectors,

Fig. 6. Simulated (a) antenna gain in different directions and (b) reflection coefficient of the patch antenna versus frequency ( $Z_{o} = 72 \Omega$ ).

this diode detector requires the radiation source to be amplitude modulated at frequency  $f_m$ . This way, the output of detector would also be located at  $f_m$ , instead of at DC, where the circuit is susceptible to flicker noise and drift. In addition, a low-noise preamplifier is also included on-chip to amplify the detected signal without significantly degrading the noise performance. The outputs of two detector cells on each side are made to share one bond pad to reduce the chip area. The diodes are biased through on-board resistor  $R_b$  (10 k $\Omega$ ), and the AC coupling capacitors  $C_1 \sim C_3$  are not integrated for their large value ( $\sim 1 \ \mu$ F). Since the Schottky diode has already been described in detail, only the design of other major components of the detector is discussed in the following sections.

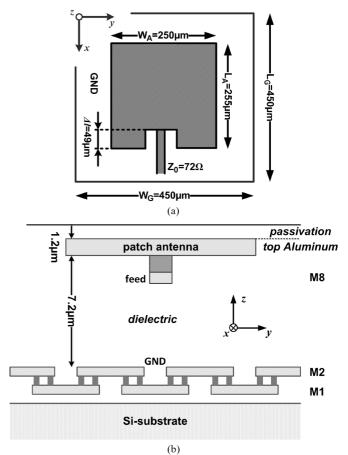

# A. On-Chip Antenna

The radiated signal is picked up by an on-chip patch antenna with a size of  $255 \times 250 \ \mu m^2$ . The antenna is made of the top Aluminum layer (shown in Fig. 5). Metal 1 and Metal 2 layers are shunted together to form the ground plane ( $450 \times 450 \ \mu m^2$ ), so that the EM wave is reflected back to free space instead of propagating through the lossy silicon substrate. The dielectric layer that separates the patch and ground plane is SiO<sub>2</sub> with 7.2- $\mu$ m thickness. The slots in Metal 1 are covered over using Metal 2 (Fig. 5(b)). The antenna performance is simulated in

Fig. 7. Matching network between the on-chip antenna and Schottky diode that uses GCPW transmission lines. The length of three sections in the figure are  $L_1 = 38 \ \mu m$ ,  $L_2 = 44 \ \mu m$  and  $L_3 = 38 \ \mu m$ .

Fig. 8. HFSS-simulated reflection coefficient and power transfer loss of the matching network.

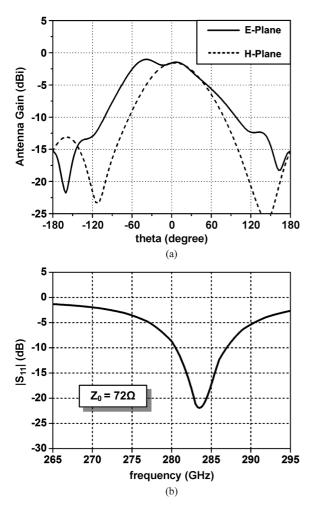

the full-wave 3-D simulator, HFSS. The other three antennas with proper port termination are also included in the simulation to account the aperture overlap effect [8]. The size of the ground plane in the simulation is also the same as the real chip area. Fig. 6 shows the simulation results. The simulated peak directivity and gain of each antenna are 5.1 dBi and -1.6 dBi, respectively for antenna efficiency of 21%. The low efficiency is due to the thin dielectric layer between the patch and ground limited by the metallization of the CMOS process as well as the conductor loss. The aperture size calculated from the directivity is 0.29 mm<sup>2</sup>. The simulated resonant impedance on the edge of patch is 108  $\Omega$ . This high resistance narrows the feed line width and increases loss. An inset in Fig. 5(a) is used to lower the antenna impedance to 72  $\Omega$  [21]. The simulated antenna -10 dB impedance bandwidth is 7 GHz.

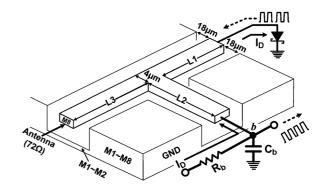

# B. Matching Network

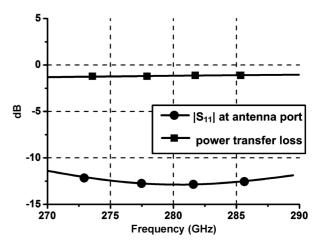

A forward-biased Schottky diode has complex impedance. To improve power transfer efficiency, a short-stub matching network is inserted between the antenna and the diode using Grounded CPW (GCPW) transmission lines (Fig. 7) [15], [22]. To match to the antenna port, the characteristic impedance of the line is also chosen to be 72  $\Omega$ . A multi-finger metal capacitor  $C_b$  connected to node "b" presents high impedance to DC bias and baseband signal, while shorting the 280-GHz signal to

Fig. 9. Schematic of the low-noise preamplifier.

ground. Since the detector performance is not sensitive to the parasitic capacitance on node "b", the diode bias current is injected and the down-converted output signal  $\Delta v$  is extracted from this node. The HFSS simulation indicates that the bandwidth of matching network is over 20 GHz and the loss is about 1.2 dB (Fig. 8).

# C. Output Combining

As mentioned earlier, the outputs of detector cells could be combined in shunt. The benefit of such configuration is the reduced output noise voltage. The expression of noise current from each detector was given in (4). If m diode detectors are connected in parallel, the total noise current power,  $(\overline{i_n^2})_{total}$ , will be increased by a factor of m.

$$\left(\overline{i_n^2}\right)_{total} = \sum_{k=1}^m \left(\overline{i_n^2}\right)_k = m \cdot \frac{4k_B T t_w}{R_j} \left(1 + \frac{f_N}{f}\right) \Delta f.$$

(6)

In contrast, the total noise voltage power at the output is decreased by a factor of m.

$$\left(\overline{v_n^2}\right)_{total} = \left(\overline{i_n^2}\right)_{total} \cdot R_{total}^2$$

$$= \left[m\frac{4k_BTt_w}{R_j}\left(1 + \frac{f_N}{f}\right)\Delta f\right] \left(\frac{R_j}{m}\right)^2 = \frac{\overline{v_n^2}}{m}.$$

(7)

For many applications, the radiation power density over the detector (rather than the total power) is fixed. Even in imaging applications in which a beam is focused on a detector, the spot size is still normally several times larger than a single antenna size [23] due to the Gaussian distribution property of the beam [24]. The output signal level does not change in a parallel configuration, so the SNR increases by a factor of m (or 6 dB for four cells). This however decreases the voltage responsivity by a factor of m. Since the output noise voltage amplitude in (7) decreases by  $m^{1/2}$  times, the overall NEP, which is the noise voltage divided by the voltage responsivity increases by a factor of  $m^{1/2}$ . But such output combining is still desirable in many situations because of higher SNR. For example, such configuration could be used to reduce the exposure time of each pixel with given SNR by four times, hence reducing the time required to form an image.

Fig. 10. Die photo of the 280-GHz CMOS SBD detector after mounting on a printed circuit board.

# D. Preamplifier

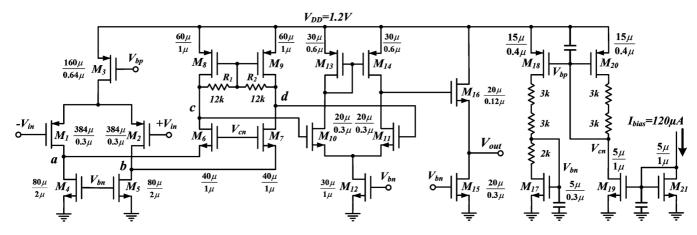

A preamplifier is included on chip and is shared among the four detector cells. The amplifier consists of three stages (Fig. 9). The first stage uses folded configuration, and has a common-centroid PMOS input pair ( $M_1$  and  $M_2$ ) to reduce the input referred flicker noise and offset. Also,  $M_4$  and  $M_5$ have a large channel length (2  $\mu$ m) to reduce their flicker noise contribution. Their large parasitic drain capacitance does not result in an unacceptably large time constant due to the low impedance at nodes "a" and "b". A pure resistive load may achieve better noise performance [25], but the large DC voltage drop across the resistors is not practical in this low- $V_{DD}$  circuit.

Fig. 11. 280-GHz detector responsivity measurement set-up.

The simulated flicker noise corner frequency and white noise level of the amplifier are 100 kHz and 3 nV/Hz<sup>1/2</sup> respectively. Resistors  $R_1$  and  $R_2$  not only provide the common-mode feedback, but also lower the time constant on nodes "c" and "d".  $M_{10} \sim M_{14}$  turn differential signals into single-ended and further boost the gain. Finally, a source follower formed with  $M_{16}$  provides sufficient driving capability for the capacitive load of instrument input. Transistors  $M_{17} \sim M_{21}$  form a bias network. The amplifier provides 50-dB voltage gain with 2-MHz 3-dB bandwidth with an external resistive feedback, which also establishes the DC operating point for the amplifier. The power consumption of amplifier is 1.3 mW at 1.2-V supply voltage.

# **IV. MEASUREMENT RESULTS**

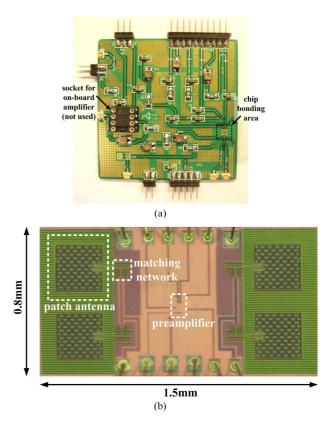

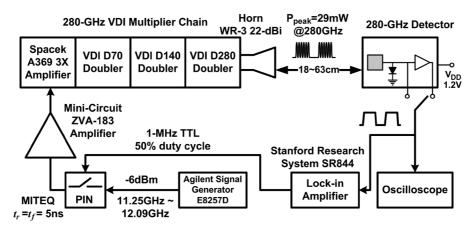

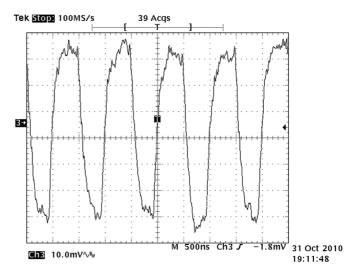

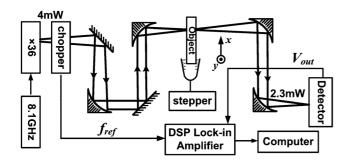

The detector is fabricated in the UMC 130-nm logic CMOS process. The chip area is  $1.5 \times 0.8 \text{ mm}^2$ . Its die photo and the printed circuit board (PCB) for testing are shown in Fig. 10. The responsivity of detector is measured using the set-up shown in Fig. 11. An input signal of 11.25 GHz ~ 12.09 GHz is fed into a VDI Amplifier/Multiplier Chain (AMC) to generate 270 GHz ~290 GHz radiation signal. Linearly-polarized RF signal is radiated through a WR-3 horn antenna. A lock-in amplifier, SR844 generates TTL signal up to 1 MHz that can turn on and off the PIN switch to AM-modulate the signal and at the same time measures the rms value of output voltage for the detector. The detector output is also measured by an oscilloscope and Fig. 12 shows the output waveform (detector at a distance of 38 cm from the source).

If the detector is placed too close to the radiation source (e.g.  $\sim 2$  cm), significant fluctuation of the amplitude in the detector output was observed in the frequency response [18]. Such standing-wave effect may be caused by the multi-reflection between the non-absorbent detector board and the source horn. The incident wave to the detector is constructively and destructively interfered. Larger separation results in smoother detector frequency response due to increased propagation loss for multi-reflected signals. Fortunately, with the higher available radiation power ( $\sim 29$  mW at 280 GHz) than the one in [18], the distance between the source and PCB in the set-up in Fig. 11 could be increased sufficiently (d = 57 cm) to significantly

Fig. 12. Waveform at the output of the preamplifier (fRF = 280.6 GHz, fchop = 1 MHz, distance = 38 cm).

reduce the standing wave effect. The detector output at varying radiation frequencies is measured with the lock-in amplifier.

The estimation expression of the single detector unit voltage responsivity is

$$\Re_v = \frac{v_{out}}{P_{in}} = \frac{\frac{\pi}{\sqrt{2}} V_{rms}}{A_R \cdot \frac{P_{cw} \cdot G_T}{4\pi d^2}}.$$

(8)

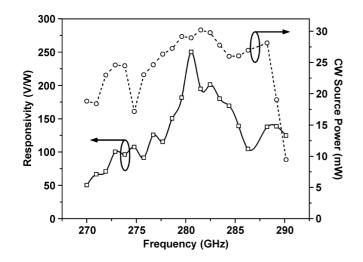

The denominator of (8) is the RF power received by each detector cell, which is the product of the aperture size,  $A_R$ , of the patch antenna from the simulations discussed in Section III and the radiation power density at a distance d from the source. The power ( $P_{cw}$  in (8)) of the transmitted continuous-wave signal (without modulation) from the source at different frequencies is measured using an Erickson PM4 power meter and plotted in Fig. 13. When the carrier amplitude is modulated by a square wave with a 50% duty cycle, Fourier analysis indicates that the rms value of fundamental frequency component of the detected signal,  $V_{rms}$  measured by the lock-in amplifier should be  $\pi/\sqrt{2} \approx 2.2$  times smaller than the peak-to-peak value of the

Fig. 13. (a) Single detector unit responsivity (with amplifier gain de-embedded) at varying source frequencies and (b) continuous-wave radiation power measured with a power meter.

square wave captured by the oscilloscope [26]. The gain of the source horn antenna,  $G_T$ , is 22 dBi.

Using (8), the voltage responsivity versus frequency is calculated and plotted also in Fig. 13 (with the 50-dB gain of the on-chip amplifier de-embedded for convenient comparison with other works). The peak responsivity 250 V/W (or 80 kV/W with on-chip amplification) is measured at 280.6 GHz, which is the resonant frequency of the patch antenna. The associated amplified detector output  $V_{rms}$  read from the lock-in amplifier is 11.9 mV, and the peak power received by the patch antenna is 0.33  $\mu$ W.

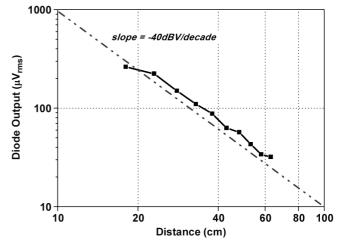

The above estimation assumes that the transmission of radiation power follows the Friis Equation [27]. To verify this assumption, the detector response (without preamplifier) at varying distances (18 to 63 cm) is also characterized. The results are shown in Fig. 14. The -40 dB/decade slope within the measurement distance range indicates that (8) is valid. The data are also consistent with prior measurements (Fig. 12 with d = 38 cm and Fig. 13 with d = 57 cm).

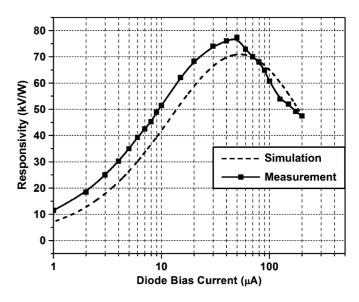

In addition, Fig. 15 plots both the measurement and simulation results of responsivity at varying diode DC current. Two curves fit well and give the same optimum bias point ( $\sim 50 \,\mu A$ ) for the peak responsivity. Power matching is most efficient at this peak point and (2) explains the rapid drop of the curve beyond the peak.

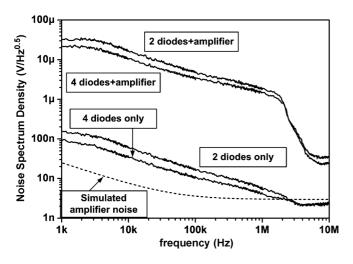

To determine the noise equivalent power (NEP) of the detector, the output noise of the detectors with and without the amplification of the on-chip amplifier is amplified by an external low-noise amplifier (EG&G Model 5184, 0.8 nV/Hz<sup>1/2</sup> input referred noise, 60-dB gain), and measured by an Agilent 89410 A vector signal analyzer. The noise power spectral density (PSD) of the detector is plotted in Fig. 16. The average noise voltage difference between two diodes in shunt and four in shunt is about 3 dB, which is consistent to (7). The 1/f noise corner frequency is around 4 MHz, which is unfortunately still larger than the maximum modulation frequency

Fig. 14. The diode output voltage versus distance between the source and detector. The measurement frequency is 280.6 GHz. The slope of -40 dB/decade for the data (or -20 dB/decade for the input power) verifies the  $1/d^2$  dependency expected from the Friis transmission equation [27].

Fig. 15. Simulation and measurement results of the single detector unit responsivity (with amplifier) versus diode bias current at 280.6 GHz input frequency.

(1 MHz) capability of the setup in Fig. 11. At 1 MHz, the output noise voltage of four detector cells is  $4.1 \text{ nV/Hz}^{1/2}$ . So each detector cell generates ~ $8.2 \text{ nV/Hz}^{1/2}$  noise. Based on the measured responsivity and noise data, the NEP of four and two detector combinations at 1-MHz modulation frequency are 66 pW/Hz<sup>1/2</sup> and 42 pW/Hz<sup>1/2</sup>, and the estimated NEP for a single cell is 33 pW/Hz<sup>1/2</sup>. When the on-chip amplifier is included, the NEP increases by approximately 10% to 73 pW/Hz<sup>1/2</sup> and 47 pW/Hz<sup>1/2</sup> for four and two detector combinations. Given that the simulated input referred noise of the amplifier at 1 MHz is 3 nV/Hz<sup>1/2</sup>, the NEP of one detector cascaded by the amplifier is estimated to be 36 pW/Hz<sup>1/2</sup>. Fig. 16 also indicates that the NEP of the detector (without amplifier) is expected to further drop to 20 pW/Hz<sup>1/2</sup>, if the modulation frequency is increased beyond the flicker noise

Fig. 16. Measured output noise voltage power spectrum density of the detector, with and without the on-chip amplifier. The bandwidth of the amplifier is 2 MHz. Simulated input referred noise of the amplifier is also plotted.

Fig. 17. Block diagram of the THz imaging system.

corner frequency of 4 MHz; and the performance starts to be limited by the noise and bandwidth of the preamplifier.

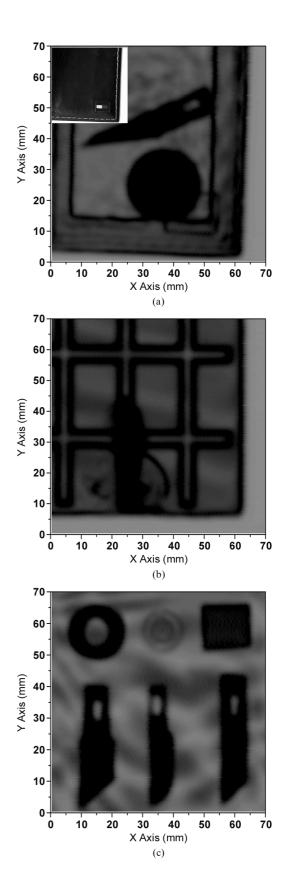

Lastly, the 280-GHz Schottky diode detector was integrated into a 2-D focal-plane image scanner at the Université Montpellier 2, France (shown in Fig. 17). The power radiated from the source (different from the one in Fig. 11) is 4 mW, and the power delivered to the detector is 2.3 mW. The lowest frequency provided by the source is 292 GHz, at which the responsivity of the detector degrades significantly (Fig. 13). Moreover, the mechanical chopper frequency of the set-up is only 340 Hz, at which the detector suffers from a high level of flicker noise (Fig. 16). Despite these, the detector is still able to form images with an SNR of 48 dB. The SNR here is defined as the ratio of quantized lock-in amplifier outputs when the detector is illuminated by the source without an object in the beam line and when the beam is blocked by a thick metal layer. Fig. 18 shows some of these images. The scanned area over the objects is  $70 \times 70 \text{ mm}^2$  divided into  $175 \times 175$  pixels. It takes around 20 minutes to scan each image. Each pixel takes 40 ms of measurement time of which mechanical motion consumes 30 ms. Since the actual electronic sampling time for noise averaging is only 10 ms, an array of detectors may also be used to construct a video-rate millimeter-wave camera. Lastly, the sampling time could be greatly reduced by optimizing the radiation and modulation frequencies.

Fig. 18. Three THz images formed using the diode detector at 292 GHz: (a) a coin and a blade hidden inside a leather wallet; (b) a blade hidden inside a chocolate bar; (c) metal and plastic rings, rubber and three blades in a shipping envelope. The bright and dark interference fringes are due to the etalon effect resulting from the reflection between two surfaces of structure that encloses the imaged objects [23].

Reference

SUMMARY OF DETECTOR PERFORMANCE AND COMPARISON WITH PRIOR WORKS

Technology

NEP

Freq.

Monolithic

[pW/Hz<sup>1/2</sup>]

[kV/W]

[THz]

Integration

4 detectors in shunt

66<sup>+</sup>

0.063<sup>+</sup>

Integration

TABLE I

| Technology                    |                                                    |                              | [pW/Hz <sup>1/2</sup> ]                                            | [kV/W]                                                               | [THz]       | Integration | Reference |

|-------------------------------|----------------------------------------------------|------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------|-------------|-------------|-----------|

| SBD                           | 130-nm<br>logic CMOS <sup>1</sup>                  | 4 detectors in shunt         | 66 <sup>†</sup><br>73 <sup>††</sup>                                | $0.063^{\dagger} \\ 20^{\dagger\dagger}$                             | 0.28        | yes         | This Work |

|                               |                                                    | 2 detectors in shunt         | $\begin{array}{c} 42^{\dagger} \\ 47^{\dagger\dagger} \end{array}$ | $0.125^{\dagger} \\ 40^{\dagger\dagger}$                             |             |             |           |

|                               |                                                    | single detector <sup>2</sup> | $33^{\dagger}$<br>$36^{\dagger\dagger}$                            | $\begin{array}{c} 0.25^{\dagger} \\ 80^{\dagger\dagger} \end{array}$ |             |             |           |

|                               | GaAs                                               |                              | 20<br>1.5                                                          | $0.4^{\dagger} \\ 3.8^{\dagger}$                                     | 0.8<br>0.15 | no          | [10]      |

|                               | ErAs/InAlGaAs                                      |                              | 1.4                                                                | $6.8^{\dagger}$                                                      | 0.1         | no          | [11]      |

| Heterojunction Backward Diode | InAs/AlSb/Al <sub>0.12</sub> Ga <sub>0.88</sub> Sb |                              | 0.18                                                               | 49.7                                                                 | 0.094       | no          | [12]      |

| MOSFET <sup>3</sup>           | Silicon                                            |                              | $100^{\dagger}$                                                    | $0.033^{\dagger}$                                                    | 0.7         | yes         | [6]       |

|                               | 250-nm CMOS                                        |                              | 300 <sup>††</sup>                                                  | $80^{\dagger\dagger}$                                                | 0.65        | yes         | [8]       |

|                               | 65-nm SOI CMOS                                     |                              | $50^{\dagger}$                                                     | $\begin{array}{c} 1.1^{\dagger} \ 72^{\dagger\dagger} \end{array}$   | 0.65        | yes         | [9]       |

| Golay Cell                    |                                                    |                              | 200-400                                                            | 0.1-45                                                               | 0.2-30      | no          | [28]      |

| Pyroelectric                  |                                                    |                              | 400                                                                | $150^{\dagger\dagger}$                                               | 0.1-30      | no          | [29]      |

<sup>†</sup>without amplifier <sup>††</sup>with amplifier

Note:

1. Simulated antenna pattern and aperture size (larger than the detector physical size) are used in (8) to estimate NEP and  $\Re_{v}$ .

2. The single detector NEP data is based on measured noise floor of two and four detectors in shunt, and calculation using Equation (7).

3. The peak responsivity and minimum NEP in [6], [8] and [9] don't occur at the same bias point.

#### V. CONCLUSIONS

This paper has shown that bulk CMOS-compatible Schottky barrier diodes can be used to detect millimeter-wave and potentially THz radiation. The performance of detector is summarized in Table I and compared to those of other room temperature THz detectors. Because of the differences in the tuned frequency, it is difficult to make a clean comparison. However, the NEP of Schottky diode detector is better than that of Golay cells and Pyroelectric detectors around 300 GHz. After de-embedding the on-chip antenna and matching network loss ( $\sim 8 \text{ dB}$ ), the estimated intrinsic NEP of the 8-cell PGS SBD in 130-nm CMOS at 280-GHz RF frequency and 4 MHz modulation frequency is 3.2 pW/Hz<sup>1/2</sup>, which is only 2× larger than that of the waveguide-fed GaAs SBD in [10] at 150 GHz. There are also several potential reasons to expect the NEP of Schottky diode detector to be lower than that of NMOS detectors including the higher current responsivity due to stronger nonlinearity of the SBD. The current power spectral density of shot noise for NMOS transistors biased in sub-threshold region of operation with  $V_{DS} = 0$  is  $4k_BTg_{ds}$  [30] compared to  $2nk_BTg_m$  of the SBD. Lastly, the capacitance of NMOS detector structures is mostly related to gate oxide capacitance while that for the SBD detectors is related to junction capacitance. These capacitances are highly bias dependent and more work is needed to understand how they contribute to the difference of responsivity and NEP for the NMOS and SBD detectors. Simulations suggest that at 600 GHz the degradation factor,  $\xi$  of this high- $f_{\rm T}$  diode only increases to 38% from 22% at 280 GHz, the loss of the matching network increases to 1.7 dB, while simulated efficiency of the patch antenna at 600 GHz (size:  $126 \times 124 \ \mu m^2$ ) improves from 21% to 50%. Because of these, the performance of diode detector should remain almost the same at 600 GHz and could be

better than that of the NMOS detectors [6], [8] including that fabricated using 65-nm CMOS on a high resistivity substrate [9]. Given that the cut-off frequency of PGS SBDs is 2 THz, detectors operating at frequencies higher than 1 THz should be possible in the 130-nm CMOS process. Lastly, the transmission imaging configuration described in this paper can be used to image hidden defects, to monitor moisture contents during paper production, to inspect envelops for dangerous contents, as well as others.

#### ACKNOWLEDGMENT

The authors are grateful to Dr. C. Mao of Integrated Device Technology, Dr. S. Sankaran and Dr. E. Seok of Texas Instruments, and Dongha Shim of the University of Florida, for their pioneering work in CMOS Schottky diodes. The authors would also like to thank Prof. E. Afshari and O. Momeni of Cornell University for the helpful discussion.

#### REFERENCES

- P. H. Siegel, "Terahertz technology," *IEEE Trans. Microw. Theory Tech.*, vol. 50, no. 3, pp. 910–928, Mar. 2002.

- [2] M. Tonouchi, "Cutting-edge terahertz technology," *Nature Photonic 1*, no. 2, pp. 97–105, Feb. 2007.

- [3] S. E. Clark, J. A. Lovberg, C. A. Martin, and V. Kolinko, "Passive millimeter-wave imaging for airborne and security applications," in *Proc. SPIE*, 2003, vol. 5077, pp. 16–21.

- [4] M. Dyakonov and M. Shur, "Shallow water analogy for a ballistic field effect transistor: New mechanism of plasma wave generation by dc current," *Phys. Rev. Lett.*, vol. 71, no. 15, pp. 2465–2468, Oct. 1993.

- [5] W. Knap, F. Meziani, N. Dyakonova, N. Lusakowski, F. Boeuf, T. Skotnicki, D. Maude, S. Rumyantsev, and M. S. Shur, "Plasma wave detection of sub-terahertz and terahertz radiation by silicon field-effect transistors," *Appl. Phys. Lett.*, vol. 85, no. 4, p. 675, 2004.

- [6] R. Tauk, F. Teppe, S. Boubanga, D. Coquillat, W. Knap, Y. M. Meziani, C. Gallon, F. Boeuf, T. Skotnicki, C. Fenouillet-Beranger, D. K. Maude, S. Rumyantsev, and M. S. Shur, "Plasma wave detection of terahertz radiation by silicon field effects transistors: Responsivity and noise equivalent power," *Appl. Phys. Lett.*, vol. 89, p. 253511, 2006.

- [7] A. Lisauskas, U. Pfeiffer, E. Öjefors, P. H. Bolivar, D. Glaab, and H. G. Roskos, "Rational design of high responsivity detectors of terahertz radiation based on distributed self-mixing in silicon field-effect transistors," *J. Appl. Phys.*, vol. 105, no. 11, p. 114511, 2009.

- [8] E. Öjefors, U. R. Pfeiffer, A. Lisauskas, and H. G. Roskos, "A 0.65 THz focal-plane array in a quarter-micron CMOS process technology," *IEEE J. Solid-State Circuits*, vol. 44, no. 7, Jul. 2009.

- [9] E. Öjefors, N. Baktash, Y. Zhao, and U. Pfeiffer, "Terahertz imaging detectors in a 65-nm CMOS SOI technology," in *Proc. 36th European Solid-State Circuits Conf.*, 2010.

- [10] J. L. Hesler and T. W. Crowe, "Responsivity and noise measurements of zero-bias Schottky diode detectors," in *Proc. 18th Int. Symp. Space Terahertz Techn.*, Pasadena, CA, Mar. 2007.

- [11] E. R. Brown, A. C. Young, J. Zimmerman, H. Kazemi, and A. C. Gossard, "High-sensitivity, quasi-optically-coupled semimetal-semiconductor detectors at 104 GHz," in *Proc. SPIE*, 2006, vol. 6212, p. 621205.

- [12] Z. Zhang, R. Rajavel, P. Deelman, and P. Fay, "Sub-micro area heterojunction backward diode millimeter-wave detectors with 0.18 pW/Hz<sup>1/2</sup> noise equivalent power," *IEEE Microw. Wireless Compon. Lett.*, vol. 21, no. 5, pp. 267–269, 2011.

[13] S. Sankaran and K. K. O, "Schottky barrier diodes for millimeter wave

- [13] S. Sankaran and K. K. O, "Schottky barrier diodes for millimeter wave detection in a foundry CMOS process," *IEEE Electron Dev. Lett.*, vol. 26, no. 7, pp. 492–494, Jul. 2005.

- [14] E. Seok, C. Cao, S. Sankaran, and K. K. O, "A mm-wave Schottky diode detector in 130-nm CMOS," in *Symp. VLSI Circuits*, Honolulu, HI, Jun. 2006, pp. 178–179.

- [15] C. Mao, C. S. Nallani, S. Sankaran, E. Seok, and K. K. O, "125-GHz diode frequency doubler in 0.13- μm CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 5, May 2009.

- [16] S. Sankaran, C. Mao, E. Seok, D. Shim, C. Cao, R. Han, C. Hung, and K. K. O, "Towards terahertz operation of CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, San Francisco, CA, 2009, pp. 202–203.

- [17] E. Seok, D. Shim, C. Mao, R. Han, S. Sankaran, C. Cao, W. Knap, and K. K. O, "Progress and challenges towards terahertz CMOS integrated circuits," *IEEE J. Solid-State Circuits*, vol. 45, no. 8, pp. 1554–1564, Aug. 2010.

- [18] R. Han, Y. Zhang, D. Coquillat, J. Hoy, H. Videlier, W. Knap, E. R. Brown, and K. K. O, "280-GHz Schottky diode detector in 130-nm digital CMOS," in *Proc. IEEE Custom Integrated Circuits Conf.*, San Jose, CA, 2010.

- [19] A. M. Cowley and H. O. Sorensen, "Quantitative comparison of solidstate microwave detectors," *IEEE Trans. Microw. Theory Tech.*, vol. 14, no. 12, pp. 588–602, Dec. 1966.

- [20] A. van der Ziel, "Noise in solid-state devices and lasers," *Proc. IEEE*, vol. 58, no. 8, pp. 1178–1206, 1970.

- [21] W. L. Stutzman and G. A. Thiele, Antenna Theory and Design, 2nd ed. New York: Wiley, 1998.

- [22] K. Jaewon, B. Jung, P. Cheung, and R. Harjani, "Novel CMOS low-loss transmission line structure," in *Proc. IEEE Radio and Wireless Conf.*, 2004, pp. 235–238.

- [23] A. Dobroiu, M. Yamashita, Y. N. Ohshima, Y. Morita, C. Otani, and K. Kawase, "Terahertz imaging system based on a backward-wave oscillator," *Appl. Opt.*, vol. 43, no. 30, pp. 5637–5646, 2004.

- [24] C. A. Brau, Modern Problems in Classical Electrodynamics. New York: Oxford Univ. Press, 2004.

- [25] T. H. Lee, The Design of CMOS Radio Frequency Integrated Circuits. Cambridge, U.K.: Cambridge Univ. Press, 1998.

- [26] "Understanding measurements using an oscilloscope versus a lock-in amplifier," Spectrum Detector Inc., Lake Oswego, OR, Application Note 1009 [Online]. Available: www.spectrumdetector.com

- [27] H. T. Friis, "A note on a simple transmission formula," in *Proc. IRE*, May 1946, vol. 34, no. 5, pp. 254–256.

- [28] "OAD-7 Golay Detector Operating Manual," QMC Instruments Ltd., Cardiff, U.K., Jan. 4, 2005.

- [29] Pyroelectric Detector, Product Sheet for Model SPH-62. Spectrum Detector Inc., Lake Oswego, OR [Online]. Available: www.spectrumdetector.com

- [30] Sarpeshkar, R. Delbruck, and T. Mead, "White noise in MOS transistors and resistors," *IEEE Circuits Devices Mag.*, vol. 9, no. 6, pp. 23–29, Nov. 1993.

**Ruonan Han** was born in Huhhot, China, in 1984. He received the B.Sc. degree in microelectronics from Fudan University, Shanghai, China, in 2007, and the M.Sc. degree in electrical engineering, from the University of Florida, Gainesville, FL, in 2009. Currently, he is working toward the Ph.D. degree in electrical engineering in Cornell University, Ithaca, NY.

His research is focused on sub-millimeter wave signal generation and detection through standard CMOS technology for imaging and spectroscopy

applications, which include wide-tuning VCO, passive frequency multiplier, and Schottky diode detector array.

Mr. Han won the IEEE Custom Integrated Circuits Conference (CICC) HELIC student scholarship in 2010, and was also the recipient of UF Outstanding Student Academic Award in 2008, Cornell Olin Fellowship in 2010 and Jacobs Fellowship in 2011.

Yaming Zhang received the B.S. degree from Tsinghua University, China, and the M.S. degree from Purdue University, West Lafayette, IN.

He is currently an engineer and consultant. He was with the University of Texas at Dallas. His research interest is in the general area of circuits and system design.

**Dominique Coquillat** is a CNRS Research Director at the University of Montpellier, France. Her activities in physics research encompass several topics. She was first involved in the research of diluted magnetic semiconductors before she has interests in Nanophotonics. As a visiting professor at the University of Glasgow, she initiated the research on photonic crystals based on III-V nitrides semiconductors. She has developed techniques for measuring the linear and the enhanced nonlinear properties of photonic crystal structures. She has

recently developed an interest in applying her nanophotonics expertise to Terahertz problems. She is interested in plasma wave emission and detection of terahertz radiation and in terahertz imaging.

**Hadley Videlier** received the Master degree from Lyon University, France, in 2007, and the Ph.D. degree from the University of Montpellier, France, in 2010.

His research focuses on THz broadband detection with transistors in room temperature, behavior of the detection in high magnetic field and low temperature, and fabrication process of transistor.

**Wojciech Knap** received the Master and Ph.D. degrees from the Faculty of Physics, Warsaw University, Poland. His Ph.D. work concerned the Terahertz (far infrared) properties of narrow gap semiconductors HgTe and InSb.

After his Master degree, he obtained a permanent Assistant Professor position at the University of Warsaw Solid State Physics Department. In 1987 he went to France and worked at University of Montpellier, Grenoble High Magnetic Field Laboratory and Toulouse Pulsed High Magnetic Field

Laboratory. In 1992 he obtained a permanent position at French National

Center for Scientific Research—CNRS—Montpellier. Between 1999 and 2001 he worked (sabbatical) in Rensellear Polytechnic Institute at group of Prof. M. Shur. He also obtained a long term grant from Japan Society of Promotion of Science and spent a year in Prof. T. Otsuji's group in Tohoku University from 2007 to 2008. His main scientific interests and activities are: i) far infrared-FIR (terahertz) properties of semiconductors: investigation of absorption, detection and emission of Far Infrared (THz) radiation by free and shallow impurity bound carriers, ii) quantum phenomena in transport: weak localisation and anti-localisation and ballistic behaviour in low dimensional systems and iii) terahertz plasma excitations in nanotransistors.

**Elliott Brown** (F'00) received the Ph.D. in applied physics from the California Institute of Technology in 1985. He did his post-doctoral work at Lincoln Laboratory, Massachusetts Institute of Technology.

He is a Professor in physics and electrical engineering where he holds the Ohio Research Scholars Endowed Chair in THz Sensors Physics. He is conducting research and teaching courses in RF and THz technology, and in solid-state and materials physics and engineering. His THz research encompasses several topics including ultra-low-noise rectifiers, ultra-

fast photoconductive sources, THz interaction with biomaterials, and THz remote sensor and imager design and simulation. Prior to WSU Dr. Brown was a Professor of Electrical and Computer Engineering at the University of California, (Santa Barbara and Los Angeles campuses), and prior to that was a Program Manager at DARPA in the Electronics Technology Office, Arlington, VA.

Dr. Brown is a Fellow of the IEEE (since 2000) and a Fellow of the American Physical Society (since 2007). In 1998 he received an Award for Outstanding Achievement from the U.S. Office of the Secretary of Defense.

Kenneth K. O received the S.B., S.M., and Ph.D. degrees in electrical engineering and computer science from the Massachusetts Institute of Technology, Cambridge, in 1984, 1984, and 1989, respectively.

From 1989 to 1994, he worked at Analog Devices Inc. developing sub-micron CMOS processes for mixed-signal applications and high speed bipolar and BiCMOS processes for RF and mixed signal applications. He was a Professor at the University of Florida, Gainesville, from 1994 to 2009. Currently, he is the Texas Instruments Inc. Distinguished Chair

Professor in Analog Circuits and Systems at the University of Texas, Dallas, and the director of SRC Texas Analog Center of Excellence. His research group (Silicon Microwave Integrated Circuits and Systems Research Group) is developing circuits and components required to implement analog and digital systems operating between 1 GHz and 1 THz using silicon IC technologies.

Dr. O was the general chair of the 2001 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM). He has served as an associate editor for IEEE TRANSACTION ON ELECTRON DEVICES from 1999 to 2001. Dr. O has also served as the publication chairman of the 1999 International Electron Device Meeting. He is elected to the IEEE Solid-State Circuits Society Adcom in 2008. He has authored/co-authored 200 journal and conference publications, and holds ten patents. He received the 1996 NSF Early Career Development Award and 2003 UF Ph.D./Mentor Award. He was also a UF Research Foundation Professor from 2004 to 2007.