#### A 110-to-130GHz SiGe BiCMOS Doherty Power Amplifier with Slotline-Based Power-Combining Technique Achieving >22dBm Saturated Output Power and >10% Power Back-Off Efficiency

**Xingcun Li<sup>1,3</sup>**, Wenhua Chen<sup>1</sup>, Shuyang Li<sup>1</sup>, Huibo Wu<sup>1</sup>, Xiang Yi<sup>2</sup>, Ruonan Han<sup>3</sup>, Zhenghe Feng<sup>1</sup>

<sup>1</sup>Tsinghua University, Beijing, China

<sup>2</sup>South China University of Technology, Guangzhou, China

<sup>3</sup>Massachusetts Institute of Technology, Boston, MA

### **Self Introduction**

Xingcun Li

Ph.D. student (2017-Present)

Tsinghua University, Beijing, China

#### Visiting student (2020)

Massachusetts Institute of Technology (MIT), Boston, MA

#### B.S. degree (2013-2017)

University of Electronic Science and Technology of China (UESTC), Chengdu, China

#### Research interests

Silicon-based mm-Wave and THz integrated circuits for radar and wireless communication.

### Outline

#### Motivation

- Power Combining Doherty PA Architecture

- Slotline-based Power Combiner

- Circuit Implementation

- Measurements

### Outline

#### Motivation

- Power Combining Doherty PA Architecture

- Slotline-based Power Combiner

- Circuit Implementation

- Measurements

#### Conclusion

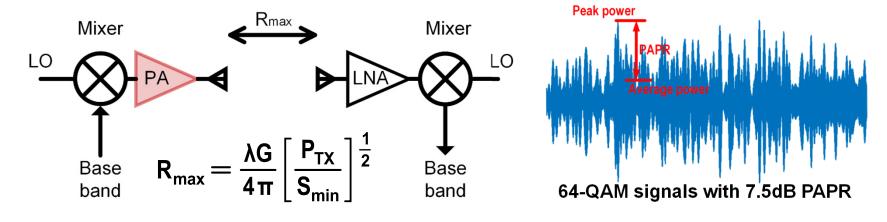

- Beyond 5G, the increasing demand for 100+Gbps data rates requires a broad available spectrum. (D-band is attractive)

- High output power (P<sub>TX</sub>) is required for a large link distance. (The high output power amplifier (PA) plays an important role)

- Peak and power back-off (PBO) efficiency enhancement is desirable for high peak-to-average power ratio (PAPR) signals. (PBO efficiency needs to be improved)

[Smartcitiesworld.net]

International Solid-State Circuits Conference

© 2022 IEEE

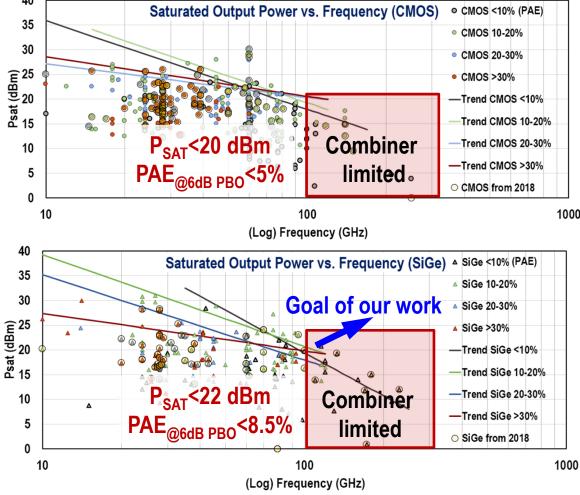

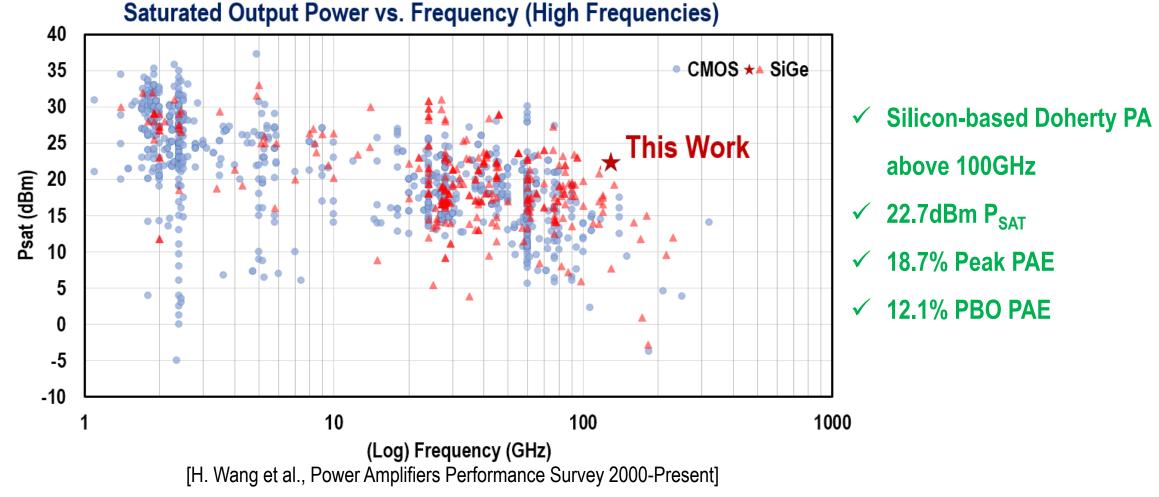

#### • Existing silicon-based sub-THz PA solutions

- High integration with other blocks

- ✓ Low-cost

- X Limited output power P<sub>OUT</sub>

- X Limited peak/PBO efficiency

- Emerging solutions for sub-THz PA

- Low-loss power combining technique with PBO efficiency enhancement

- [H. Wang et al., Power Amplifiers Performance Survey 2000-Present]

© 2022 IEEE International Solid-State Circuits Conference

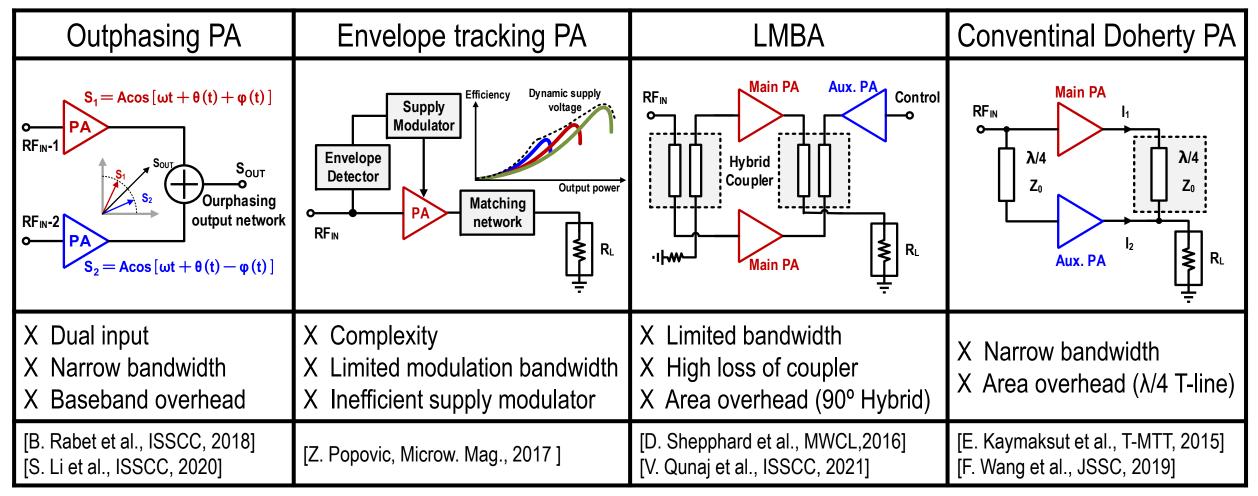

#### PBO efficiency enhancement techniques

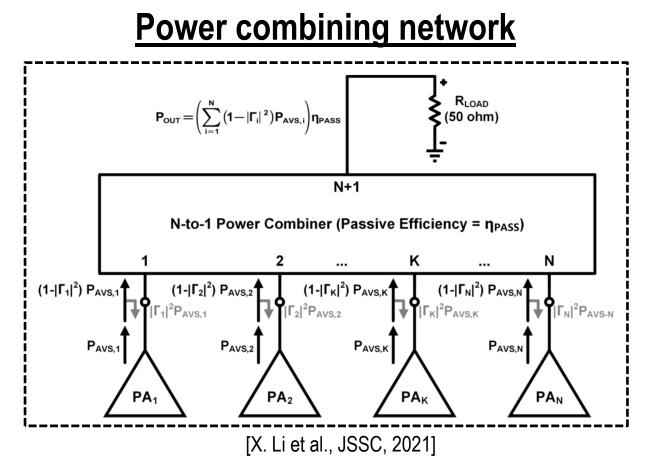

• Low-loss power combiner/matching networks

#### **Two factors affect the power loss:**

• Reflection at the input port:

Passive efficiency (n<sub>PASS</sub>) of the combiner:

Conductor loss

Dielectric loss

Combiner Structure

Radiation loss

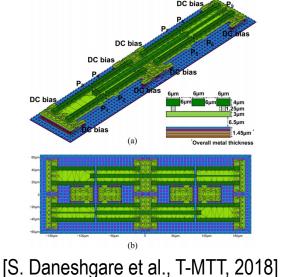

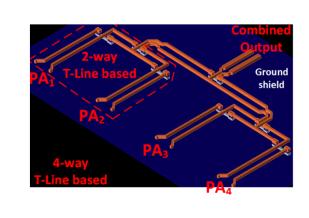

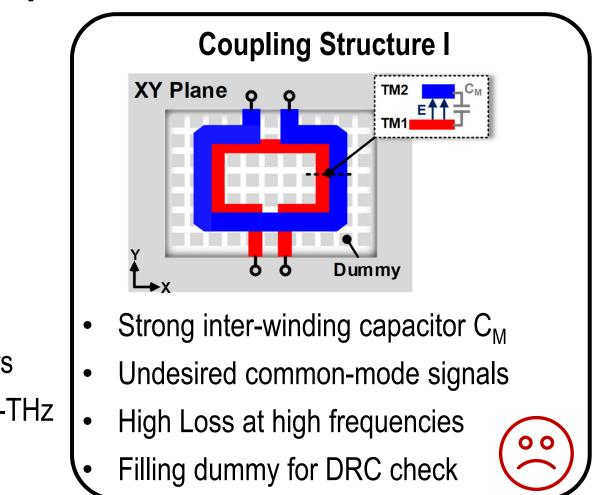

- Existing silicon-based sub-THz power combiner

- Low-loss combining

- No PBO efficiency enhancement

Three-conductor combiner

[B. Philippe et al., ISSCC, 2020]

-opt

Transformer-based combiner

PA1 (+)

PA2 (-)

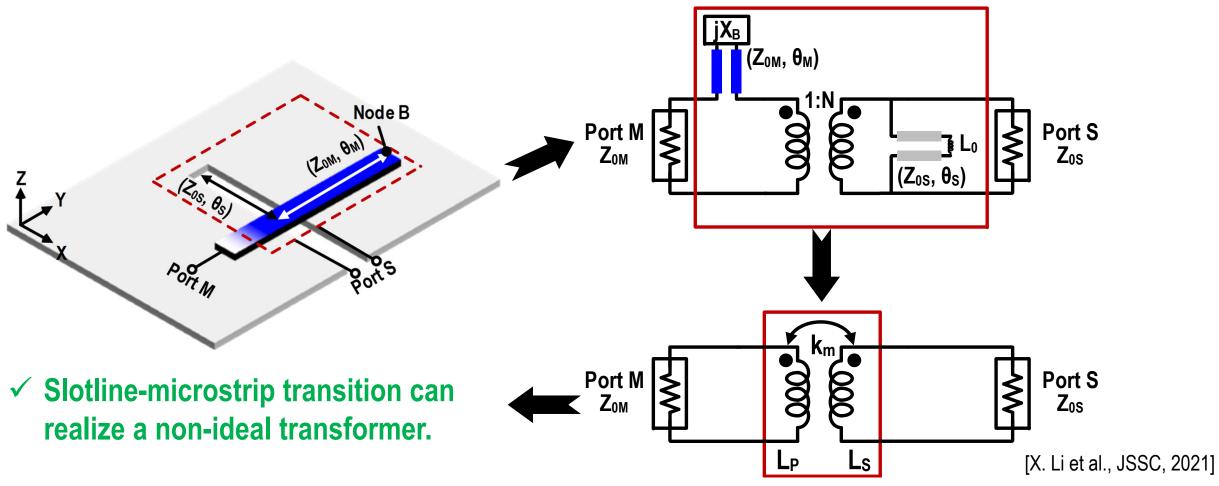

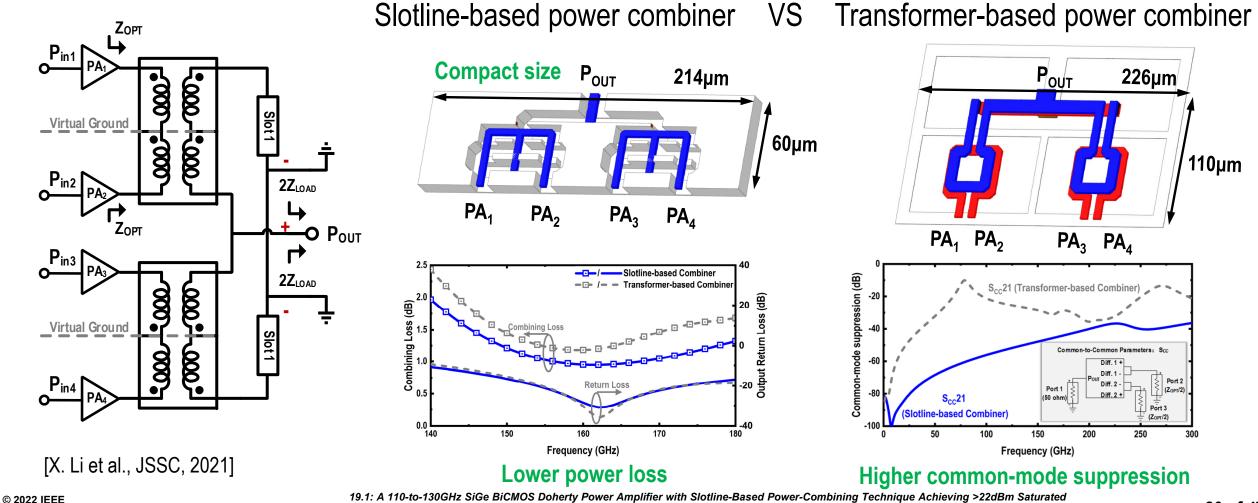

Slotline-based combiner

XZ Plan

19.1: A 110-to-130GHz SiGe BiCMOS Doherty Power Amplifier with Slotline-Based Power-Combining Technique Achieving >22dBm Saturated Output Power and >10% Power Back-Off Efficiency PA3 (-)

<sup>[</sup>X. Li et al., JSSC, 2021]

### Outline

#### Motivation

- Power Combining Doherty PA Architecture

- Slotline-based Power Combiner

- Circuit Implementation

- Measurements

#### Conclusion

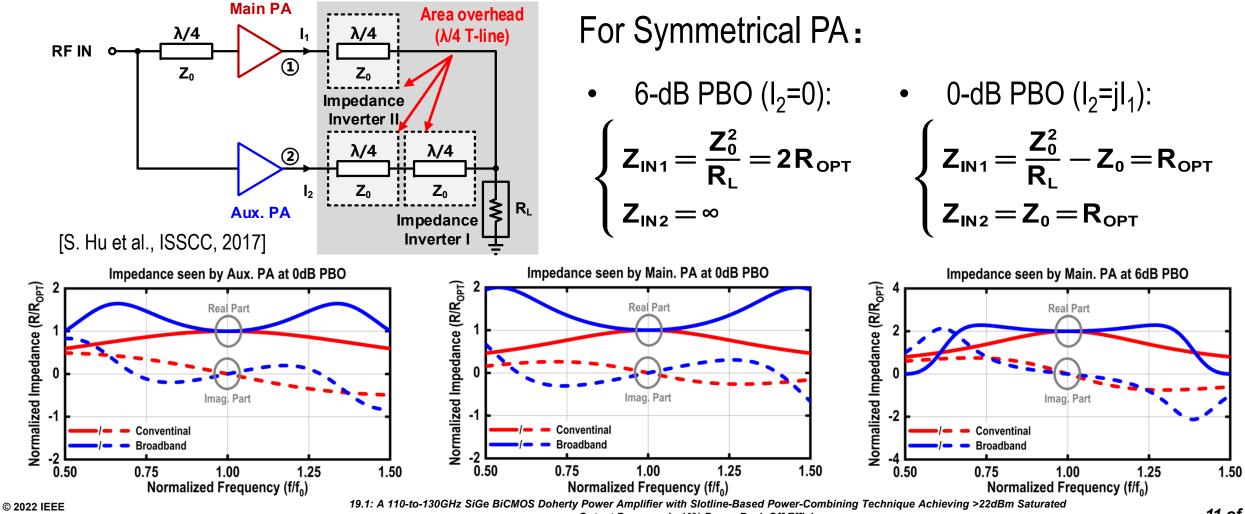

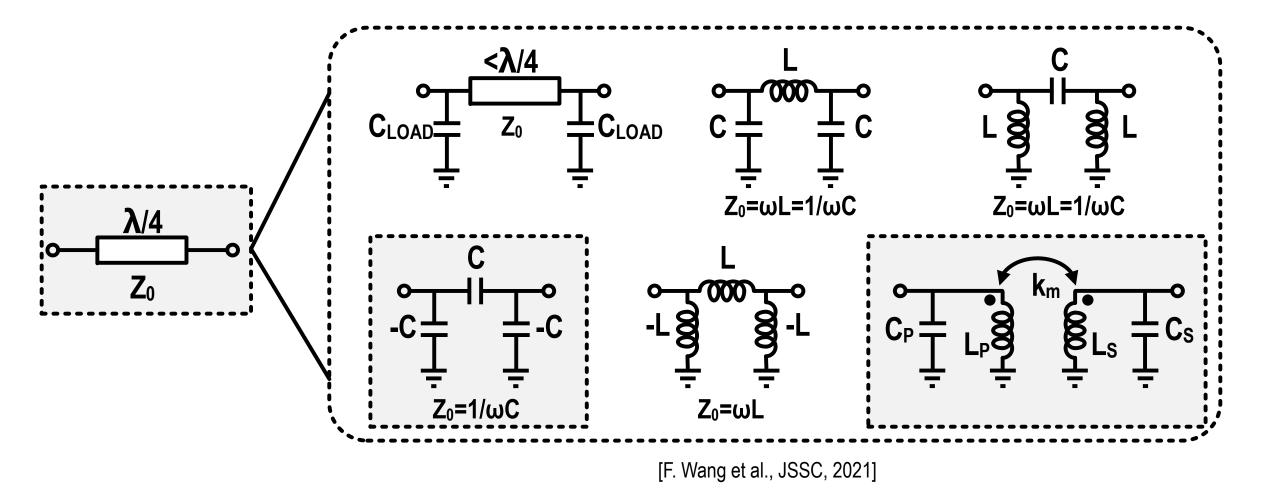

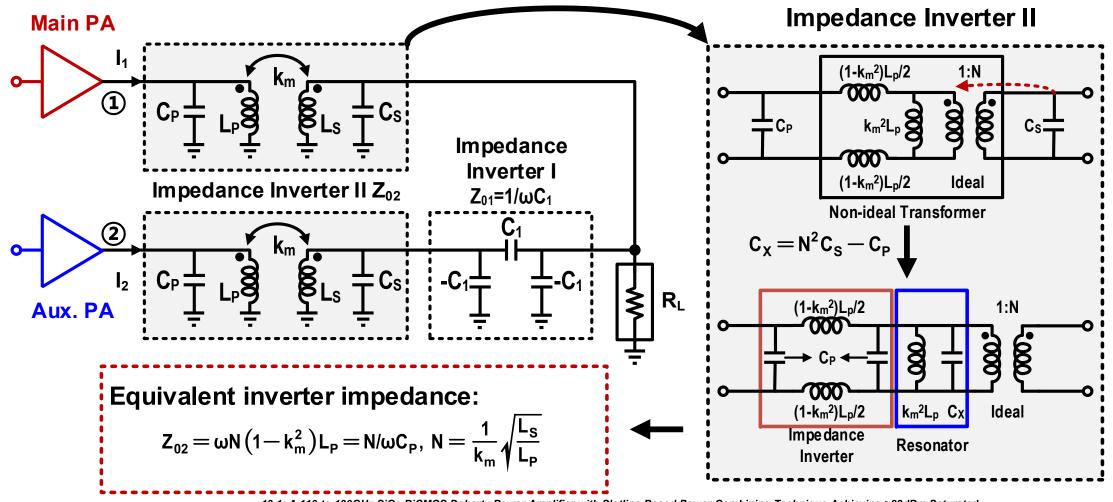

• Broadband Doherty PA with two impedance inverters

International Solid-State Circuits Conference

Output Power and >10% Power Back-Off Efficiency

• Compact impedance inverters

Broadband Doherty PA with compact inverters

© 2022 IEEE International Solid-State Circuits Conference

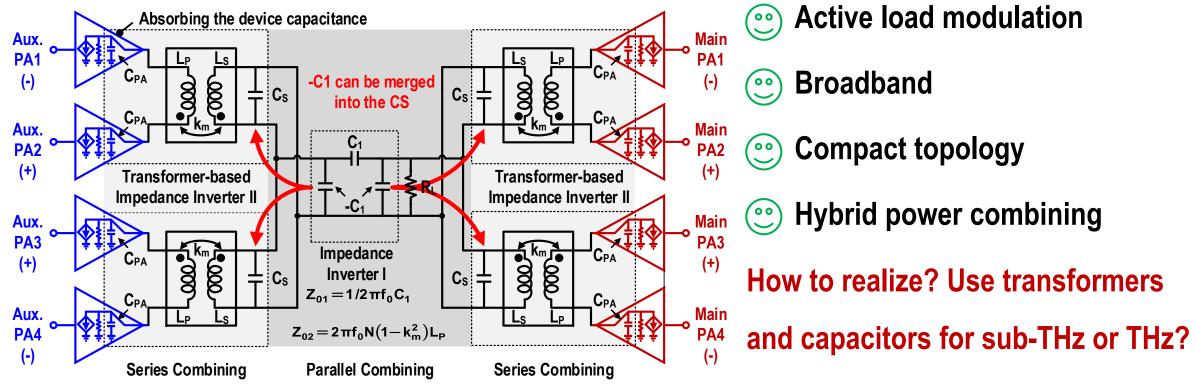

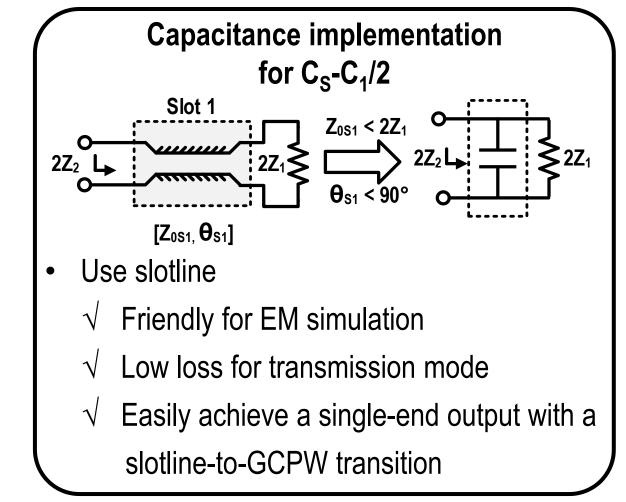

#### • Power combining Doherty PA architecture

- ✓ Absorb the device capacitance  $C_{PA}$

- ✓  $-C_1$  can be absorbed into  $C_S$

© 2022 IEEE International Solid-State Circuits Conference

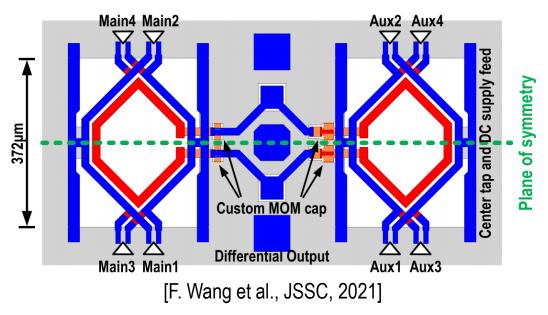

• Conventional transformer-based implementation for mm-wave PA

- Differential output

- X Lossy differential line

- X Unfriendly for testing

- Many MOM capacitors

- X Unfriendly for sub-THz EM simulation

### Outline

#### Motivation

- Power Combining Doherty PA Architecture

- Slotline-based Power Combiner

- Circuit Implementation

- Measurements

#### Conclusion

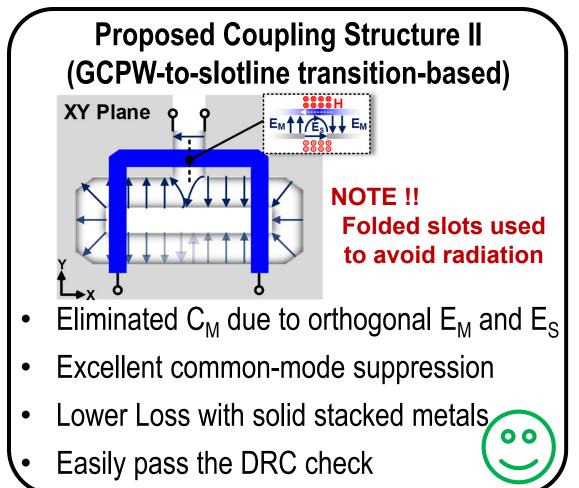

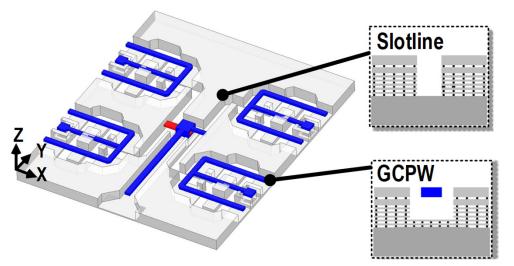

#### **Slotline-based Power Combiner Microstrip-to-slotline transition structure** Odd-mode: Even-mode: TM-mode wave at the slotline is suppressed Transmission mode at the slotline is excited Node / **Undesired common-mode** $\checkmark$ signals can be suppressed Forward Current - Return Current - Electric Field by the slotline.

Microstrip-to-slotline transition structure

Slotline-based power combiner implementation

• Slotline-based power combiner implementation

International Solid-State Circuits Conference

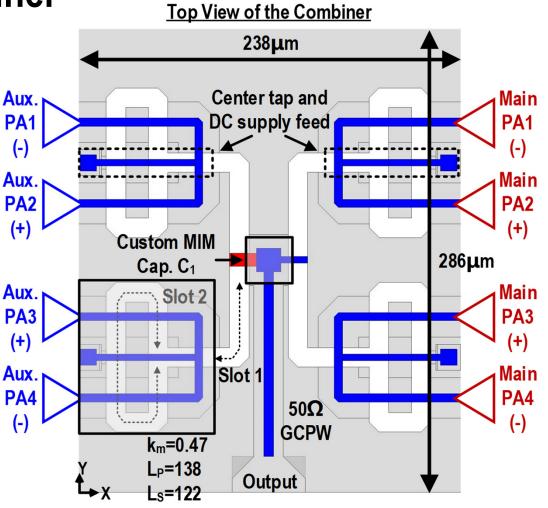

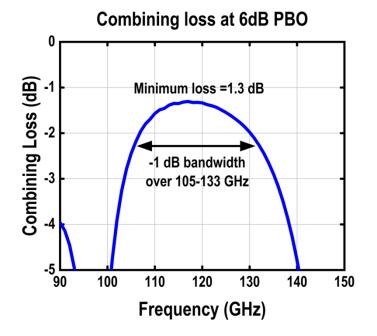

#### • Slotline-based Doherty power combiner

- ) 8-way hybrid (parallel-series) power combining

- Less capacitor

- Single-end output

- Compact layout

#### **3D EM Simulation Model**

© 2022 IEEE International Solid-State Circuits Conference

- Slotline-based Doherty power combiner

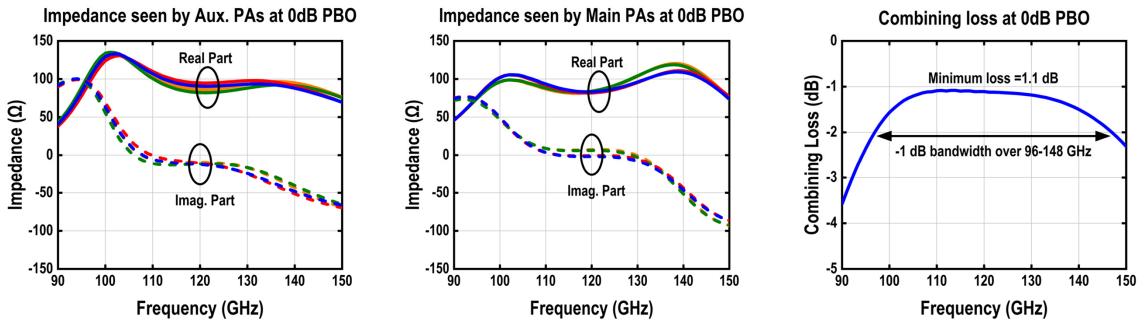

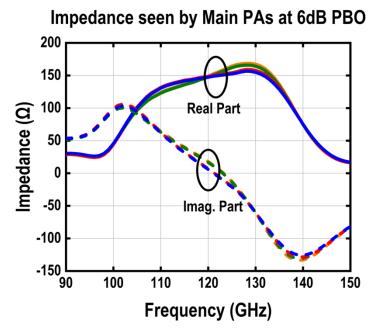

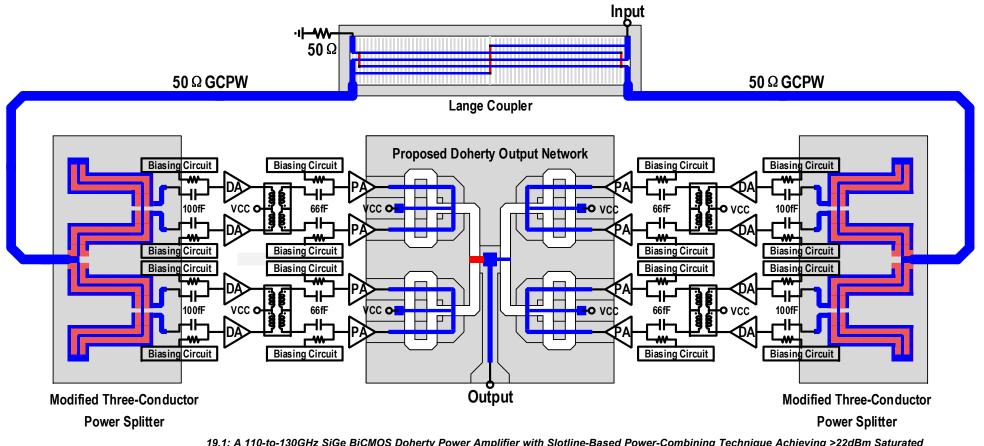

- Full EM simulations at 0dB power back-off

- ✓ Small port impedance difference

- $\checkmark$  Broadband and low-loss power combining

- Slotline-based Doherty power combiner

- Full EM simulations at 6dB power back-off

- ✓ Small port impedance difference

- $\checkmark$  Broadband and low-loss power combining

### Outline

#### Motivation

- Power Combining Doherty PA Architecture

- Slotline-based Power Combiner

- Circuit Implementation

- Measurements

#### Conclusion

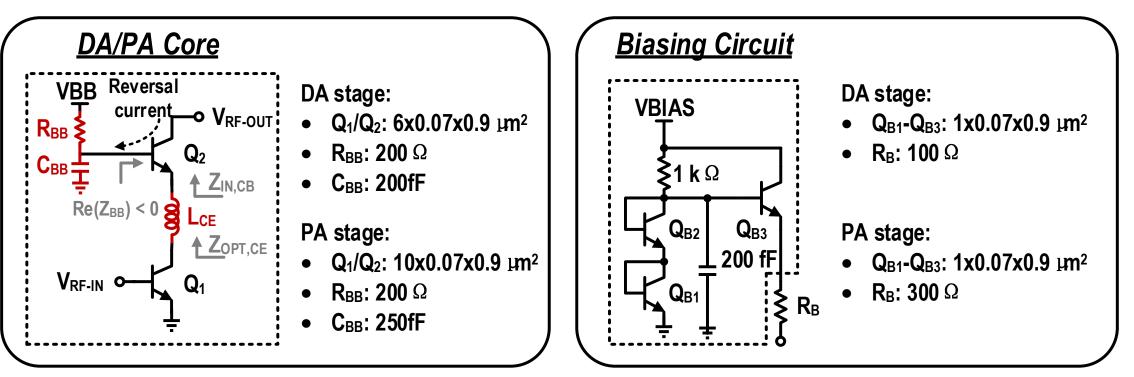

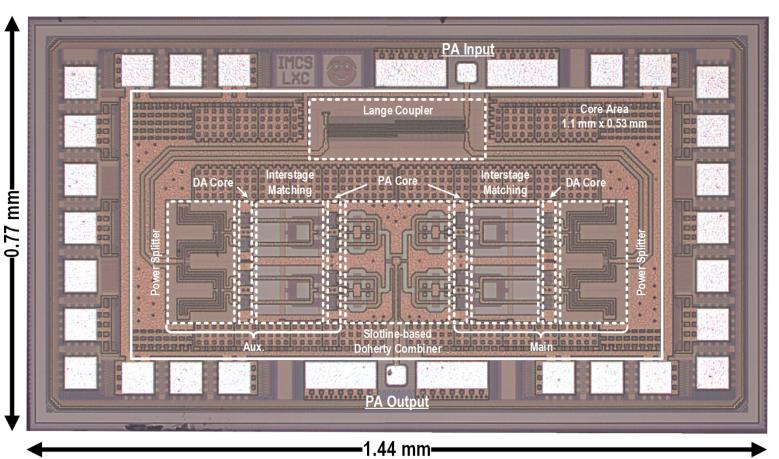

- Top schematic

- ✓ 0.13µm SiGe BiCMOS:  $f_T/f_{max}$ =350/450GHz

#### • Top schematic

- ✓ Stacked DA/PA stages: VCC=4V

- ✓ Linear-bias circuit

#### • Top schematic

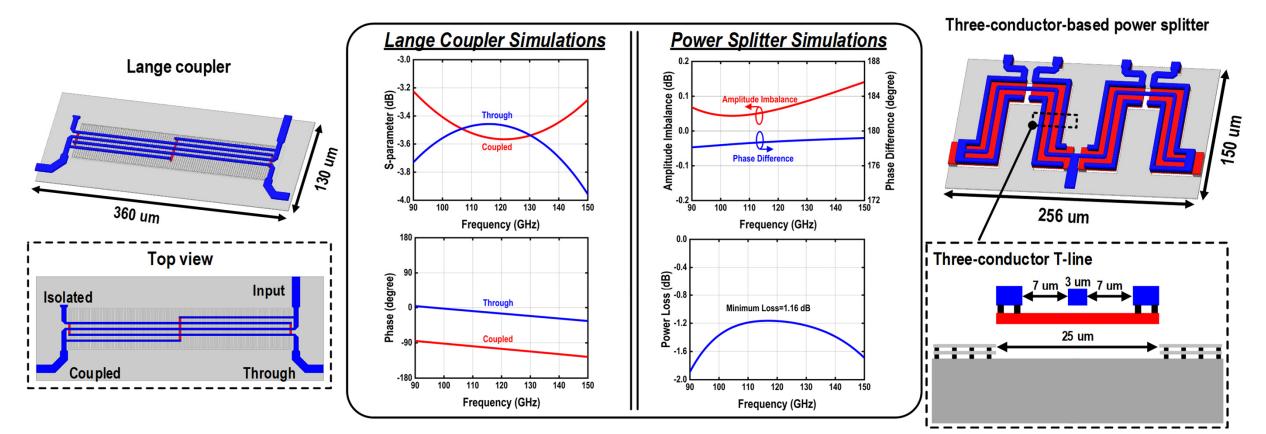

✓ Power splitting and phase shifting: Lange coupler+three-conductor-based balun.

- Chip microphotograph and package module

- 1.11mm<sup>2</sup> total chip size

- 0.58mm<sup>2</sup> core area

Package module

### Outline

#### Motivation

- Power Combining Doherty PA Architecture

- Slotline-based Power Combiner

- Circuit Implementation

#### Measurements

#### Conclusion

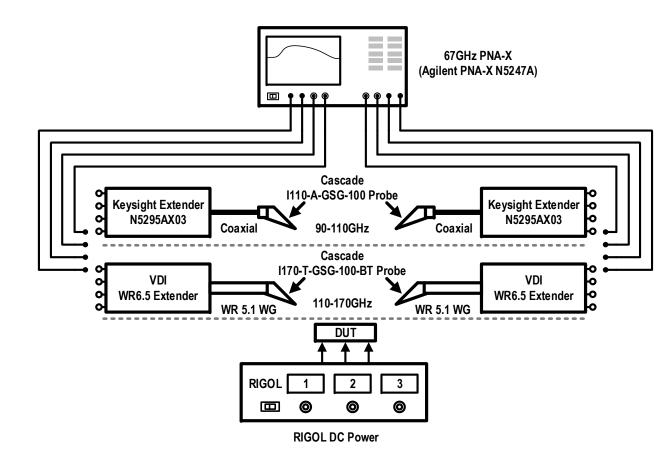

• S-parameter measurement setup

#### 90-110GHz S-parameters

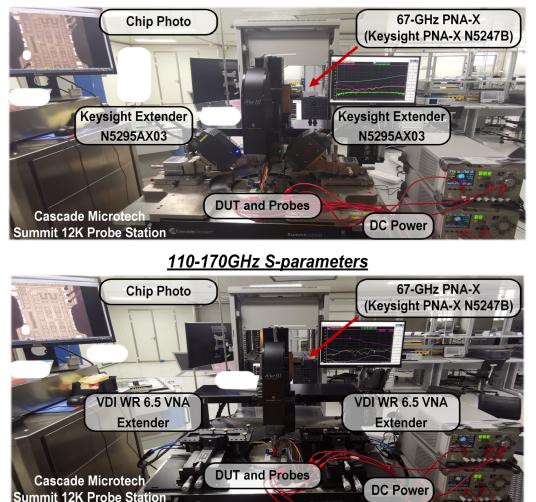

• S-parameter measurement results

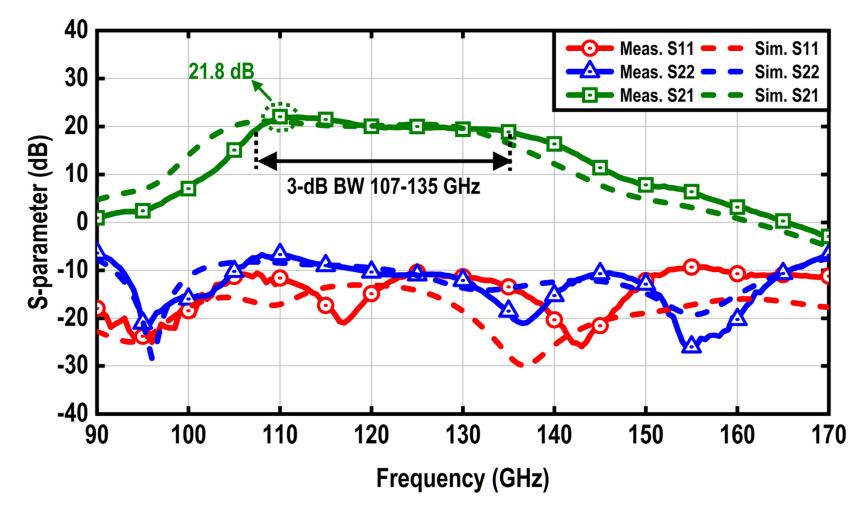

• Large-signal measurement setup

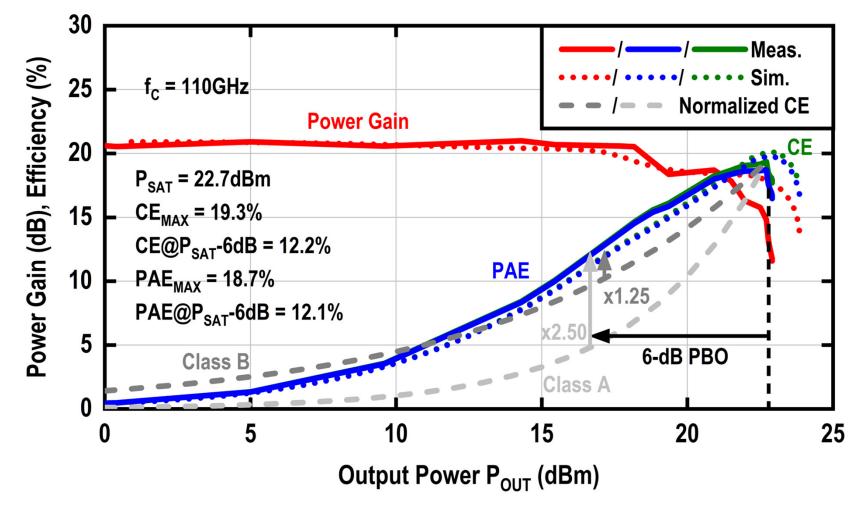

• Large-signal continuous-wave measurement results at 110GHz

© 2022 IEEE International Solid-State Circuits Conference

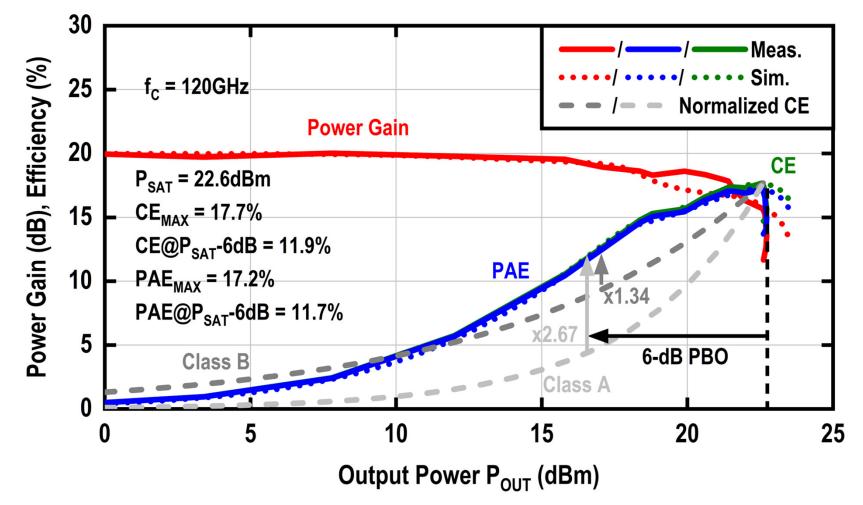

• Large-signal continuous-wave measurement results at 120GHz

© 2022 IEEE International Solid-State Circuits Conference

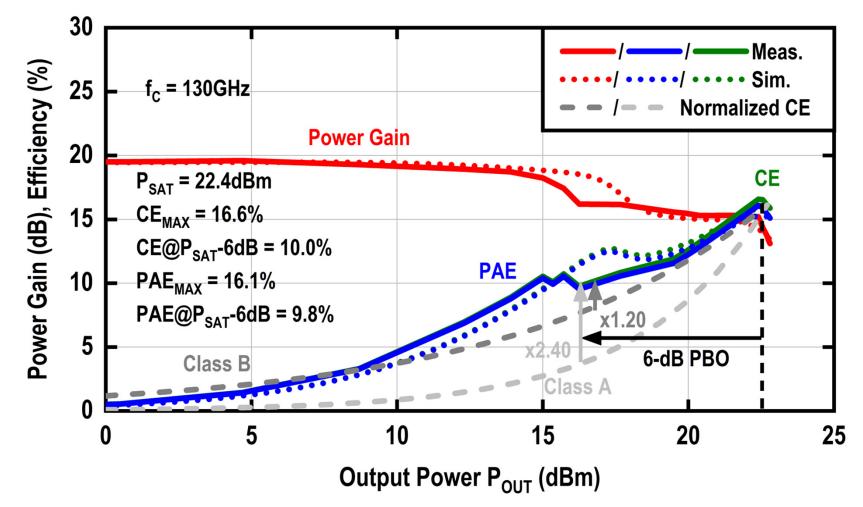

• Large-signal continuous-wave measurement results at 130GHz

© 2022 IEEE International Solid-State Circuits Conference

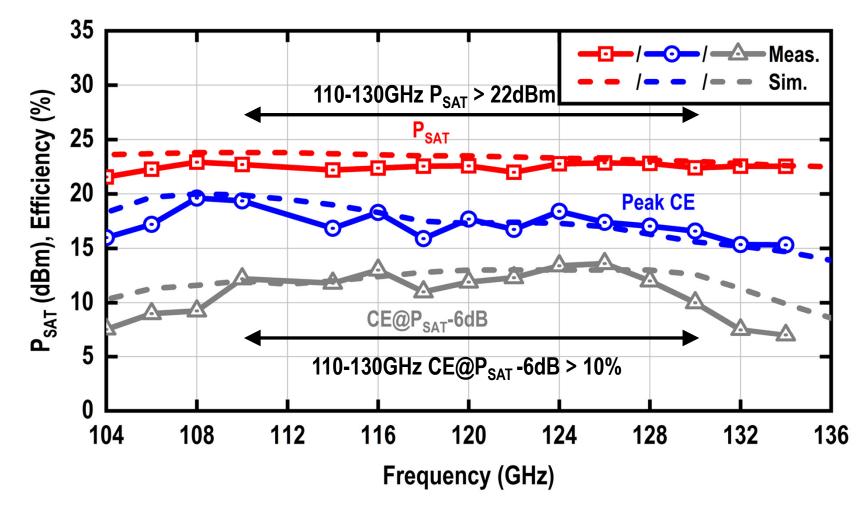

• Large-signal continuous-wave performance over frequency

<sup>19.1:</sup> A 110-to-130GHz SiGe BiCMOS Doherty Power Amplifier with Slotline-Based Power-Combining Technique Achieving >22dBm Saturated Output Power and >10% Power Back-Off Efficiency

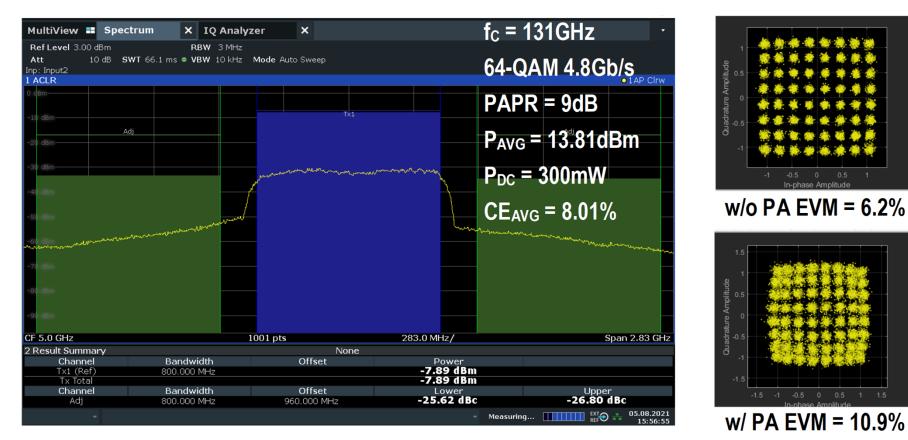

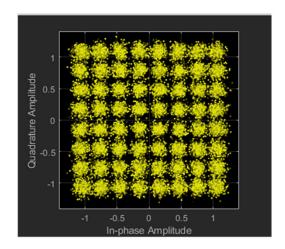

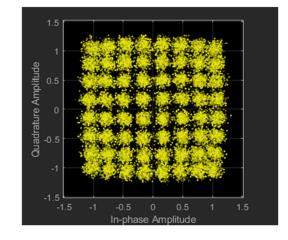

#### • Large-signal modulation measurement results

✓ 4.8Gb/s single-carrier 64-QAM signal with a 9dB PAPR

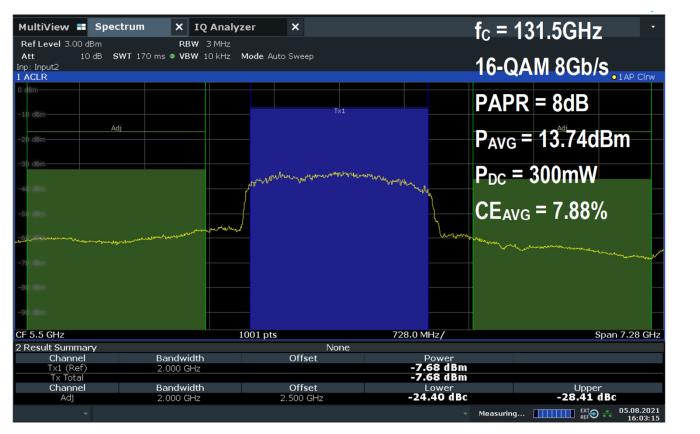

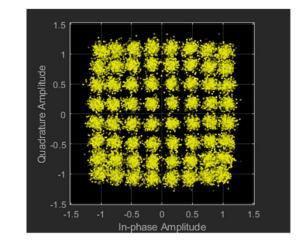

#### • Large-signal modulation measurement results

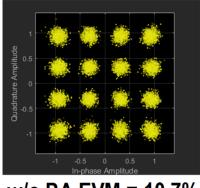

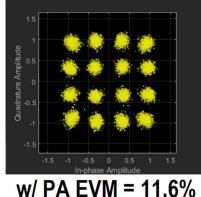

✓ 8Gb/s single-carrier 16-QAM signal with a 8dB PAPR

w/o PA EVM = 10.7%

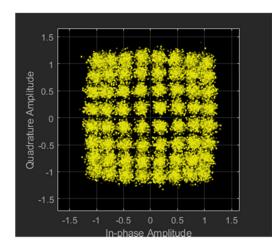

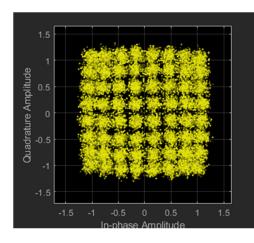

• Large-signal modulation measurement results

w/o PA EVM = 9.9%\*

fc=131.5GHz 64-QAM 1.6GSym/s (9.6Gb/s) PAPR=9dB

w/ PAw/ PA $P_{AVG} = 12.65 dBm$  $P_{AVG} = 13.88 dBm$  $CE_{AVG} = 6.39\%$  $CE_{AVG} = 8.14\%$ EVM = 10.5\%EVM = 12.4%

\*The EVM performance of high-order and wideband modulated signals is limited by the Tx module.

© 2022 IEEE International Solid-State Circuits Conference

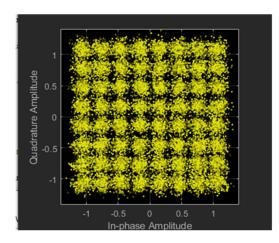

• Large-signal modulation measurement results

w/o PA EVM = 11.0%\*

fc=131.5GHz 64-QAM 2GSym/s (12Gb/s) PAPR=9dB

w/ PAw/ PA $P_{AVG} = 12.49dBm$  $P_{AVG} = 13.76dBm$  $CE_{AVG} = 6.16\%$  $CE_{AVG} = 7.92\%$ EVM = 11.1%EVM = 11.9\%

\*The EVM performance of high-order and wideband modulated signals is limited by the Tx module.

© 2022 IEEE International Solid-State Circuits Conference

### Outline

#### Motivation

- Power Combining Doherty PA Architecture

- Slotline-based Power Combiner

- Circuit Implementation

- Measurements

#### • Comparison with the state-of-art D-band PAs

| Reference                | This Work                                |      | Philippe<br>ISSCC'20 | Li<br>RFIC'21              | Petricli<br>MWCL'21        |                    | Rao<br>MWCL'21     | Li<br>JSSC'21               |                                  |  |

|--------------------------|------------------------------------------|------|----------------------|----------------------------|----------------------------|--------------------|--------------------|-----------------------------|----------------------------------|--|

| Technology               | 130nm SiGe                               |      |                      | 16nm FinFET                | 45nm CMOS<br>SOI           | 55nm SiGe          |                    | 90nm SiGe                   | 130nm SiGe                       |  |

| Architecture             | 8-way<br>Slotline-based<br>Comb. Doherty |      |                      | 4-way<br>TF-based<br>Comb. | 8-way<br>TL-based<br>Comb. | Common-base        |                    | 4-way<br>Wilkioson<br>Comb. | 4-way<br>Slotline-based<br>Comb. |  |

| Gain (dB)                | 21.8                                     |      |                      | 25.6                       | 24                         | 24                 | 22.4               | 18.2                        | 30.7                             |  |

| BW <sub>-3dB</sub> (GHz) | 28<br>(107 to 135)                       |      |                      | 22                         | 21<br>(130 to 151)         | 34<br>(125 to 159) | 25<br>(125 to 150) | 35<br>(110 to 145)          | 40<br>(142 to 182)               |  |

| Freq. (GHz)              | 110                                      | 120  | 130                  | 135                        | 140                        | 135                | 135                | 130                         | 161                              |  |

| P <sub>SAT</sub> (dBm)   | 22.7                                     | 22.6 | 22.4                 | 15                         | 17.5                       | 17.6               | 19.3               | 21.9                        | 18.1                             |  |

| PAE <sub>MAX</sub> (%)   | 18.7                                     | 17.2 | 16.1                 | 12.8                       | 13.4                       | 17.5               | 13                 | 12.5                        | 12.4                             |  |

| PAE at 6-dB PBO (%)      | 12.1                                     | 11.7 | 9.8                  | <5*                        | <5*                        | 8.5                | 6.7                | <5*                         | <5*                              |  |

| Area (mm <sup>2</sup> )  | 1.11 (0.58**)                            |      |                      | 0.041**                    | 0.43**                     | 0.18**             | 0.26**             | 1.71                        | 0.42                             |  |

© 2022 IEEE International Solid-State Circuits Conference 19.1: A 110-to-130GHz SiGe BiCMOS Doherty Power Amplifier with Slotline-Based Power-Combining Technique Achieving >22dBm Saturated

Output Power and >10% Power Back-Off Efficiency

• Output power comparison with the state-of-art silicon-based PAs

<sup>© 2022</sup> IEEE International Solid-State Circuits Conference

#### • Comparison with prior mm-wave Doherty PAs and D-band Txs

| Reference               | This                                  | s Work                    | Wang<br>JSSC'21                    | Liu<br>IMS'21                | Kaymaksut<br>T-MTT'15           | Hamani<br>SSCL'20                            |                                              |

|-------------------------|---------------------------------------|---------------------------|------------------------------------|------------------------------|---------------------------------|----------------------------------------------|----------------------------------------------|

| Technology              | 130n                                  | ım SiGe                   | 130nm SiGe                         | 130 nm SiGe                  | 40 nm CMOS                      | 45 nm CMOS SOI                               |                                              |

| Architecture            | · · · · · · · · · · · · · · · · · · · | otline-based<br>. Doherty | Multi-Primary<br>DAT-based Doherty | Quadrature-Hybrid<br>Doherty | 8-way TF-based<br>Comb. Doherty | Tx Front-End<br>(IF AMP+LO+Mixer+PA)         |                                              |

| Modulation Scheme       | 64-QAM                                | 16-QAM                    | 64-QAM                             | 64-QAM                       | 64-QAM                          | 16-QAM<br>8 Channels                         | 64-QAM<br>8 Channels                         |

| Freq. (GHz)             | 131                                   | 131.5                     | 28                                 | 54                           | 72                              | CH5: 150.7                                   | CH5: 150.7                                   |

| Data Rate (Gb/s)        | 4.8                                   | 8                         | 1.2                                | 6                            | 0.6                             | 7.04                                         | 10.56                                        |

| PAPR (dB)               | 9                                     | 8                         | 6.5                                | 7.35                         | N.A.                            | N.A.                                         | N.A.                                         |

| P <sub>AVG</sub> (dBm)  | 13.8                                  | 13.7                      | 20.9                               | 14.6                         | 15.9                            | 0.1                                          | 0.1                                          |

| PAE <sub>AVG</sub> (%)  | 8 (CE)<br>7.9 (PAE)                   | 7.9 (CE)<br>7.8 (PAE)     | 18.4                               | 21 (CE)<br>16 (PAE)          | 7.2                             | 0.24<br>(P <sub>OUT</sub> /P <sub>DC</sub> ) | 0.24<br>(P <sub>OUT</sub> /P <sub>DC</sub> ) |

| EVM (%)                 | 10.9                                  | 11.6                      | 5.6                                | 4.7                          | 5.5                             | 6.8                                          | 8                                            |

| Area (mm <sup>2</sup> ) | 1.11                                  | (0.58**)                  | 4.19                               | 1.62                         | 0.19**                          | 2.98                                         |                                              |

© 2022 IEEE International Solid-State Circuits Conference

- Power combining Doherty PA architecture

- $\checkmark$  Achieves hybrid power combining and broadband active load modulation.

- 8-way low-loss slotline-based power combiner

- ✓ A practical alternative to the conventional transformer with a compact layout.

#### • The D-band PA

- ✓ Achieves 22.7/22.6/22.4dBm P<sub>SAT</sub> with 18.7/17.2/16.1% peak PAE and 12.1/11.7/9.8% back-off PAE at 110/120/130GHz.

- ✓ Supports 16-QAM and 64-QAM signals and achieves 13.81/13.74dBm P<sub>AVG</sub> and 8.01/7.88% CE<sub>AVG</sub>.

#### Acknowledgement

- This work was supported by the National Key Research and Development Program of China under Grant 2019YFB2204701 and the Beijing National Research Center for Information Science and Technology (BNRist).

- The authors would like to thank team members from Intelligent Microwave Circuit and System (IMCS) Lab for their technical discussion and support.

- The authors would like to thank Gaxtrem Technology (Beijing) Co., Ltd. and Beijing Innovation Center for Future Chip (ICFC) for the measurements support.

- The authors would like to thank Chengkai Wu for the test module support.

# Thanks !